Abstract

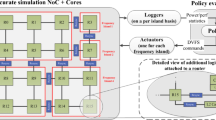

Considering the complexity of the future 4G telecommunication systems, power consumption management becomes a major challenge for the designers, particularly for base-band modem functionalities. System level low-power policies which optimize dynamically the consumption, achieve major power savings compared to low level optimisations (e.g gated clock or transistor optimisation). We present an innovative power modeling methodology of a 4G modem which allows to accurately qualify such low power solutions. Then, we show the energy savings attended by these power management methods considering silicium technology.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Kaiser, S., et al.: 4G MC-CDMA Multi Antenna SoC for Radio Enhancements. IST summit Lyon (June 2004)

Durand, Y., et al.: FAUST: On chip distributed Architecture for a 4G Baseband Modem SoC, IP-SOC Grenoble (2005)

Clermidy, F., et al.: A NoC based communication framework for seamless IP integration in Complex Systems, IP-SOC Grenoble (2005)

Lee, Y.-H., Krishna, C.M.: Voltage-Clock Scaling for Low Energy Consumption in Real Time Embedded Systems. In: Proceedings of the Real-Time Computing Systems and Applications Conference IEEE (December 1999)

Jejurika, R., Gupta, R.: Dynamic Voltage Scaling for Systemwide Energy Minimization in real time embedded Systems. In: ISLPED IEEE, Newport beach (2004)

Khouri, K.S.: Leakage Power Analysis and Reduction During Behavioral Synthesis. IEEE Transactions on VLSI systems (December 2002)

Synopsys, Prime Power, website: http://www.synopsys.com/products/power/

Berkeley University, The Ptolemy Project, website: http://ptolemy.eecs.berkeley.edu/

Easy project team, The EASY project design story 4, Easy Project IST (2004)

Sinha, A., Chandrakasan, A.: JouleTrack A web based Tool for Software energy Profiling. In: DAC IEEE (June 2001)

Liu, D., Svensson, C.: Power Consumption Estimation in CMOS VLSI Chips. IEEE Journal of Solid State Circuits (June 1994)

Simunic, T., et al.: Cycle Accurate Simulation of Energy Consumption in Embedded Systems. In: DAC IEEE, New Orleans (1999)

Chillet, D.: Basse consommation dans les systèmes embarqués, Roscoff-Ecole thématique (avril 2003)

Tiwari, V., et al.: Power analysis of Embedded Software: A first Step Towards Software Power Minimization. Transactions on VLSI systems IEEE (December 1994)

Gupta, R.: Formals Methods for Dynamic Power Management. In: ICCAD IEEE (November 2003)

Kim, W., et al.: Performance Comparison of Dynamic Voltage Scaling Algorithms for Hard Real Time Sytems. In: Proceedings of the Real-Time Computing Systems and Applications Conference IEEE (2002)

CADENCE CAD Tools, SoC Encounter design tools, website: http://www.cadence.com/products/digital_ic/soc_encounter/index.asp

Pascal, V., Edith, B.: Design of On-chip and Off-chip Interfaces for a GALS NoC Architecture. In: Proceedings of the ASYNC Conference IEEE, Grenoble (2006)

Romain, L., et al.: Performance evaluation of a NoC based design for MC-CDMA Telecommunication using NS2. In: Proceedings of the RSP Conference IEEE, Montreal (2005)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Grosse, P., Durand, Y., Feautrier, P. (2006). Power Modeling of a NoC Based Design for High Speed Telecommunication Systems. In: Vounckx, J., Azemard, N., Maurine, P. (eds) Integrated Circuit and System Design. Power and Timing Modeling, Optimization and Simulation. PATMOS 2006. Lecture Notes in Computer Science, vol 4148. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11847083_16

Download citation

DOI: https://doi.org/10.1007/11847083_16

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-39094-7

Online ISBN: 978-3-540-39097-8

eBook Packages: Computer ScienceComputer Science (R0)