## Swap and Rotate: Lightweight linear layers for SPN-based blockciphers

Subhadeep Banik<sup>1</sup>, Fatih Balli<sup>1</sup>, Francesco Regazzoni<sup>2</sup> and Serge Vaudenay<sup>1</sup>

<sup>1</sup> LASEC, Ecole Polytechnique Fédérale de Lausanne, Switzerland subhadeep.banik@epfl.ch, fatih.balli@epfl.ch, serge.vaudenay@epfl.ch

<sup>2</sup> University of Lugano, Switzerland regazzoni@alari.ch

**Abstract.** In CHES 2017, Jean et al. presented a paper on "Bit-Sliding" in which the authors proposed lightweight constructions for SPN based block ciphers like AES, PRESENT and SKINNY. The main idea behind these constructions was to reduce the length of the datapath to 1 bit and to reformulate the linear layer for these ciphers so that they require fewer scan flip-flops (which have built-in multiplexer functionality and so larger in area as compared to a simple flip-flop). In this paper, we develop their idea even further in few separate directions.

First, we prove that given an arbitrary linear transformation, it is always possible to construct the linear layer using merely 2 scan flip-flops. This points to an optimistic venue to follow to gain further GE reductions, yet the straightforward application of the techniques in our proof to PRESENT and GIFT leads to inefficient implementations of the linear layer, as reducing ourselves to 2 scan flip-flops setting requires thousands of clock cycles and leads to very high latency.

Equipped with the well-established formalism on permutation groups, we explore whether we can reduce the number of clock cycles to a practical level, i.e. few hundreds, by adding few more pairs of scan flip flops. For PRESENT, we show that 4 (resp. 8, 12) scan flip-flops are sufficient to complete the permutation layer in 384 (resp. 256, 128) clock cycles. For GIFT, we show that 4 (resp. 8, 10) scan flip flops correspond to 320 (resp. 192, 128) clock cycles. Hence our results give a good balance between throughput and circuit area, that is, we are able to construct circuits with reasonable throughput (by increasing the latency to threefold at most) and smaller than the state-of-the-art implementations of PRESENT and GIFT.

Finally, in order to provide the best of the two worlds (i.e. circuit area and latency), we push our scan flip-flop choices even further to completely eliminate the latency incurred by the permutation layer, without compromising our stringent GE budget. We show that not only 12 scan flip flops are sufficient to execute PRESENT permutation in 64 clock cycles, but also the same scan flip flops can be used readily in a combined encryption decryption circuit. Our final design of PRESENT and GIFT beat the record of Jean et al. and Banik et al. in both latency and in circuit-size metric. We believe that the techniques presented in our work can also be used at choosing bit-sliding-friendly linear layer permutations for the future SPN-based designs.

Keywords: Lightweight circuit, PRESENT, GIFT, FLIP

## 1 Introduction

The block cipher family Katan [CDK09] and then later Simon [BSS<sup>+</sup>] were in some sense aimed to achieve a lower limit of lightweight encryption in terms of area occupied in silicon. Both these ciphers have shift register based update functions, which is efficient to implement in ASIC when the length of datapath is reduced to one bit. In CHES 2017, Moradi et al. presented the concept of "Bit-Sliding" [JMPS17]. The authors proposed lightweight

constructions for SPN based block ciphers like AES [DR02], PRESENT [BKL+07] and SKINNY [BJK+16] that also had a datapath width of 1 bit. This was counter-intuitive because the block ciphers in question used 8/4-bit S-boxes and it was not immediately clear how the width of the data-path could be made smaller than the size of the S-box that the block cipher was employing. The main idea behind these constructions was to reformulate the linear layer for these ciphers so that they require fewer scan flip-flops (which have built-in multiplexer functionality at the input port and so larger in area as compared to a simple flip-flop). In particular, the PRESENT linear layer which is essentially a bit permutation over the state, was decomposed as  $P_2^4 \circ P_1$ , where  $P_1$  was a permutation that operated on each 16-bit block of the 64-bit state and  $P_2$  is some other permutation. This decomposition allowed the authors of [JMPS17] to implement the linear layer using only 25 scan flip-flops and 39 regular flip-flops, whereas previous implementations [RPLP08] have required all 64 flip-flops holding the state to have additional multiplexer at its input.

Motivation: Lightweight implementation of cryptosystems is an important application in itself, as numerous papers in literature exist in which area optimization is one of the main goals [JMPS17, MPL+11]. Moreover area minimization is crucial in applications like medical implants and passive RFID tags (that typically do not use latest CMOS technology) run on extreme tight area budgets. Moreover reducing the area footprint of a system, invariably reduces the power consumption of the system which is also an important optimizable design metric. For example, in implantable devices, peak power is a more crucial metric, as the wearer certainly can not tolerate any rise in operating temperature caused due to high power. It is however well known that most lightweight circuits (that are generally serialized) are typically not energy efficient [BBR15]. Although energy is an important metric, our research direction is directed towards applications that can not ignore area and power constraints.

We choose PRESENT and GIFT block ciphers for our analysis, because both employ bit permutations as their linear layer. Apart from this, studying these ciphers is of independent interest because of the importance of these designs in the cryptographic community. PRESENT is currently an ISO/IEC standard and an extremely popular in the security community. GIFT is used as the underlying block cipher in 6 of the 33 candidates in the second round of the NIST lightweight cryptography competition [nis].

Contribution: Thus the main idea behind [JMPS17] was that the fewer scan flip-flops one uses to construct the circuit is likely to translate into a lowering of the total hardware area of the circuit. Taking this idea forward, in this paper we try to answer the following question: is it possible to construct the linear layer if only 2 of the 64 flip-flops used to store the state are scan flip-flops? The question can be answered in the affirmative by drawing upon the theory of permutation groups and the methods presented in [Con]. However a straightforward application of the ideas in [Con] is computation intensive: for example we will subsequently show that to execute the PRESENT permutation P using just 2 scan flip-flops using the ideas in [Con] requires decomposing P into around 36000 simpler permutations which naturally take an equal number of clock cycles to implement in a flip-flop array. Hence such a construction would incur heavy lowering of throughput of the cipher which is very impractical. Much of the theory developed in this paper tries to investigate if we can speed up the execution of P in the 2 scan flip-flop setup. One of the conclusions that we draw from our investigations, is that in a two scan flip-flop set up, even with various mathematical optimization, the number of cycles taken to encrypt/decrypt is way too large to implement practically (we achieve one PRESENT/GIFT round function in 1472/1728 cycles which is still very slow). Furthermore one needs to store a large set of control bits to direct the swap operations in scan flip-flops. If only 2 scan flip-flops are used around, 200 bytes of information are needed to be stored in a lookup table in the circuit. This drives up the area requirements to the extent that our 2 scan flip-flop implementation of both PRESENT and GIFT becomes more expensive than currently reported in the literature. Thus although theoretically interesting, our findings show that the above implementation is practically counterproductive.

Therefore we investigate if adding more scan flip-flops to the circuit can significantly reduce the number of cycles/area of the circuit. Intuitively this makes sense because more scan flip-flops allow us to execute more transposition operations on the state register in a single clock cycle and hence it could reduce the total number of cycles to implement the bit permutation layer. This could lead to a much smaller size of control bits required to control swaps and keep the area to a minimum. In fact we found that adding 2 or 4 additional scan flip-flops provides us with a reasonable balance between area and throughput.

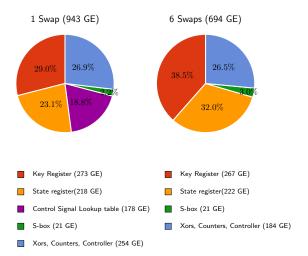

As a result of the theoretical foundations built in the paper, we construct lightweight implementations of the PRESENT and GIFT [BPP+17] circuits for both encryption (E) and combined encryption+decryption (ED) modes. Both PRESENT and GIFT are block ciphers in which the linear layer is composed with a bit permutation over the internal state. We increase the number of scan flip-flops gradually from 2 to 4 to 6 and so on and observe the reduction of both area and latency. Our smallest implementation of PRESENT at 694 GE and GIFT at 907 GE are not only the lowest reported in the literature so far, but each is achieved at only 64 clock cycles per round, which is faster than both the 68 cycle/round implementation of PRESENT in [JMPS17] and 96 cycle/round implementation of GIFT in [BPP+17]. In the ED mode, the smallest PRESENT and GIFT circuits occupy 786 GE and 1025 GE which are also the smallest reported thus far. (Note that all circuits have been synthesized with the standard cell library CORE90GPHVT v 2.1.a of the STM 90nm CMOS logic process). We take the ideas forward and look at the stream cipher FLIP [MJSC16] whose core state update function is also a bit permutation. We propose three circuits for FLIP: the first is a direct implementation of the ideas in [Con]. This version however takes time proportional to the cube of the size of the secret key to produce a single keystream bit and is hence not practical. The second circuit we construct takes quadratic time and occupies only 3581 GE. The third circuit we propose uses slightly different ideas for bit swapping and can achieve the FLIP functionality in linear time. This circuit has an area of around 8605 GE. These are the first reported hardware implementations of FLIP.

**Organization:** The paper is organized in the following manner. In Section 2, we start with some preliminary definitions and notations along with a brief sketch of the proofs presented in [Con]. The main mathematical background is then developed in Section 3. This section is mainly concerned with the PRESENT block cipher. The theory built up in this section is done in various stages: in each stage we try to decrease the number of permutations required to describe the PRESENT bit permutation. Section 4 contains a circuit level description of the cipher along with a cycle by cycle operational details of its functions. Thereafter we extend these ideas to the GIFT block cipher in Section 5. In the next sections 6 and 7, we investigate if introducing more scan flip-flops helps us construct circuits with smaller area and higher throughput. Finally, we look at the circuit construction of FLIP in Section 8. Section 9 concludes the paper.

## 2 Permutation Preliminaries

We use the symbol  $S_n$  to denote the permutation group on n elements. Naturally we have,  $|S_n| = n!$  and the group is non-commutative. A k-cycle  $\pi \in S_n$  (for  $1 \le k \le n$ ) is generally expressed as the k-tuple  $(i_1, i_2, \ldots, i_k)$  which implies

- $\pi(i_1) = i_2$ ,  $\pi(i_2) = i_3$ ,  $\cdots$ ,  $\pi(i_k) = i_1$ , and

- $\pi(i) = i, \forall i \notin \{i_1, i_2, \dots, i_k\}.$

This is a permutation of order equal to k. A transposition (or a swap)  $\tau \in S_n$  is a 2-cycle. Denote by  $\mathbb{A}_{\pi}$  the set of *active* elements in the permutation, i.e.  $\{i_1, i_2, \dots, i_k\}$ . In general,

if  $\pi$  is a composition of several cycles of different orders, then define

$$\mathbb{A}_{\pi} = \{x: \ \pi(x) \neq x\}.$$

The cycles  $\pi_1$  and  $\pi_2$  of orders  $k_1$  and  $k_2$  respectively are called disjoint if  $\mathbb{A}_{\pi_1}$  and  $\mathbb{A}_{\pi_2}$  are disjoint, i.e. have no elements in common. It is easy to see all disjoint cycles commute under the composition operation. It is well known that every permutation in  $S_n$  can be expressed as a composition of disjoint k-cycles, uniquely up to ordering of the k-cycles. To begin discussions, we cite a couple of results from [Con].

**Lemma 1.** [Con, Theorem 2.1] For  $n \geq 2$ ,  $S_n$  is generated by its transpositions.

The above is not particularly difficult to prove. We know that the identity permutation can be written as  $\tau^2$  where  $\tau$  is any transposition. As stated above, any permutation can be expressed as compositions of k-cycles, and any k-cycle  $(i_1, i_2, \ldots, i_k)$  can be written as  $(i_1, i_2) \circ (i_2, i_3) \circ \cdots \circ (i_{k-1}, i_k)$  and so the result follows.

**Lemma 2.** [Con, Theorem 2.5] For  $n \geq 2$ ,  $S_n$  is generated by the transposition (1,2) and the n-cycle  $(1,2,\ldots,n)$ .

A rigorous proof of the above lemma may be found in [Con], but for the benefit of the reader we give the sketch idea. First note that the set  $G_1 = \{(1,2), (2,3), \dots, (n-1,n)\}$  also generates  $S_n$ . That is because any arbitrary transposition (i,j) can be obtained by the composition  $(i,i+1)\circ(i+1,j)\circ(i,i+1)$ , where the first and third transpositions are already in  $G_1$ . If |i+1-j| > 1, then (i+1,j) can be further written as  $(i+1,i+2)\circ(i+2,j)\circ(i+1,i+2)$ , and so on, until the term in the middle is in  $G_1$ . Given the following identity

$$\pi \circ (i_1, i_2, \dots, i_k) \circ \pi^{-1} = (\pi(i_1), \pi(i_2), \dots, \pi(i_k)),$$

for all k-cycles and  $\pi \in S_n$ , it is possible to show that any transposition of the form (i, i+1) can be generated by (1,2) and the n-cycle  $(1,2,\ldots,n)$ . This is true since, if we denote  $\sigma = (1,2,\ldots,n)$ , then we have

$$\sigma^{i-1} \circ (1,2) \circ \sigma^{-(i-1)} = (\sigma^{i-1}(1), \sigma^{i-1}(2)) = (i,i+1).$$

This completes the proof.

## 3 Application to PRESENT

The bit-permutation layer in PRESENT is given in Table 1. The round function specifies that the i-th state bit is moved to the P(i)-th position after application of the permutation layer. Let us look at the unique decomposition of P into its disjoint k-cycles. The disjoint decomposition of P consists of a total of twenty 3-cycles, where the remaining four points are fixed. The 3-cycles are listed as follows:

- (1, 16, 4), (2, 32, 8), (3, 48, 12), (5, 17, 20), (6, 33, 24),

- $\bullet$  (7, 49, 28), (9, 18, 36), (10, 34, 40), (11, 50, 44), (13, 19, 52),

- (14, 35, 56), (15, 51, 60), (22, 37, 25), (23, 53, 29), (26, 38, 41),

- (27, 54, 45), (30, 39, 57), (31, 55, 61), (43, 58, 46), (47, 59, 62).

Let the above 3-cycles be labeled by the symbols  $c_0$  to  $c_{19}$ . Note that since all the  $c_i$ 's are disjoint, the composition of all of them in any order will result in P. Each  $c_i$  may be further expressed as a composition of two swaps:  $c_i = s_i \circ t_i$ . Table 2 lists all such decompositions explicitly.

| i    | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| P(i) | 0  | 16 | 32 | 48 | 1  | 17 | 33 | 49 | 2  | 18 | 34 | 50 | 3  | 19 | 35 | 51 |

| i    | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| P(i) | 4  | 20 | 36 | 52 | 5  | 21 | 37 | 53 | 6  | 22 | 38 | 54 | 7  | 23 | 39 | 55 |

| i    | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| P(i) | 8  | 24 | 40 | 56 | 9  | 25 | 41 | 57 | 10 | 26 | 42 | 58 | 11 | 27 | 43 | 59 |

| i    | 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| P(i) | 12 | 28 | 44 | 60 | 13 | 29 | 45 | 61 | 14 | 30 | 46 | 62 | 15 | 31 | 47 | 63 |

Table 1: Specifications of PRESENT bit-permutation layer.

| i | $c_i$        | $s_i \circ t_i$         | i  | $c_i$        | $s_i \circ t_i$         |

|---|--------------|-------------------------|----|--------------|-------------------------|

| 0 | (1, 16, 4)   | $(4,16) \circ (1,4)$    | 10 | (14, 35, 56) | $(14,35) \circ (35,56)$ |

| 1 | (2, 32, 8)   | $(8,32) \circ (2,8)$    | 11 | (15, 51, 60) | $(15,51)\circ(51,60)$   |

| 2 | (3, 48, 12)  | $(12,48) \circ (3,12)$  | 12 | (22, 37, 25) | $(25,37) \circ (22,25)$ |

| 3 | (5, 17, 20)  | $(5,17) \circ (17,20)$  | 13 | (23, 53, 29) | $(29,53)\circ(23,29)$   |

| 4 | (6, 33, 24)  | $(24,33) \circ (6,24)$  | 14 | (26, 38, 41) | $(26,38)\circ(38,41)$   |

| 5 | (7, 49, 28)  | $(28,49) \circ (7,28)$  | 15 | (27, 54, 45) | $(45,54)\circ(27,45)$   |

| 6 | (9, 18, 36)  | $(9,18) \circ (18,36)$  | 16 | (30, 39, 57) | $(30,39) \circ (39,57)$ |

| 7 | (10, 34, 40) | $(10,34) \circ (34,40)$ | 17 | (31, 55, 61) | $(31,55) \circ (55,61)$ |

| 8 | (11, 50, 44) | $(44,50) \circ (11,44)$ | 18 | (43, 58, 46) | $(46,58) \circ (43,46)$ |

| 9 | (13, 19, 52) | $(13,19) \circ (19,52)$ | 19 | (47, 59, 62) | $(47,59) \circ (59,62)$ |

Table 2: Decomposition of the 3-cycle  $c_i$ 's into swaps for the PRESENT permutation

Note that if we were to compose a permutation consisting of application of all the  $t_i$ 's (in any order) followed by application of all the  $s_i$ 's (again in any order) we would get back P. That is to say

$$P = s_{b_0} \circ s_{b_1} \circ \cdots \circ s_{b_{19}} \circ t_{a_0} \circ t_{a_1} \circ \cdots \circ t_{a_{19}},$$

where  $a_0, a_1, \ldots a_{19}$  and  $b_0, b_1, \ldots b_{19}$  are any arbitrary orderings of the set  $\{0, 1, \ldots, 19\}$ . We will prove a generalized form of the above statement in the following lemma.

**Lemma 3.** Let  $\pi$  be a permutation in  $S_n$  whose disjoint cycle decomposition consists of the cycles  $c_0, c_1, \ldots, c_{m-1}$  each with orders  $i_0, i_1, \ldots, i_{m-1}$  respectively (with  $\sum_{j=0}^{m-1} i_j = n$ ), i.e.

$$\pi = c_0 \circ c_1 \circ \cdots \circ c_{m-1}.$$

Let  $i_0 \le i_1 \le \cdots \le i_{m-1}$ . Let each  $c_j$  be expressed as composition of  $i_j - 1$  transpositions  $s_j(1), s_j(2), \ldots, s_j(i_j - 1)$ . So we have

$$s_{m-1}(i_{m-1}-1) \circ \cdots \circ \cdots \circ \cdots \circ s_{m-1}(2) \circ s_{m-1}(1) = c_{m-1}$$

$$\vdots$$

$$s_{j}(i_{j}-1) \circ \cdots \circ \cdots \circ s_{j}(2) \circ s_{j}(1) = c_{j}$$

$$\vdots$$

$$s_{0}(i_{0}-1) \circ \cdots \circ s_{0}(2) \circ s_{0}(1) = c_{0}$$

$$Sets: \chi_{i_{m-1}-1} \chi_{i_{j}-1} \chi_{i_{0}-1} \cdots \chi_{2} \chi_{1}$$

Define the set  $\chi_k = \{s_{m-1}(k), s_{m-2}(k), \ldots\}$  (for  $1 \le k < i_{m-1}$ ) as explained above. Let  $\theta_k$  be the composition of all transpositions in  $\chi_k$  in any arbitrary order. Then we must have

**A** Each  $\theta_k$  is invariant of the order in which the transpositions in  $\chi_k$  are applied.

**B** We must have  $\pi = \theta_{i_{m-1}-1} \circ \cdots \theta_{i_{j}-1} \circ \cdots \theta_{2} \circ \theta_{1}$ .

Proof. Please see Appendix A.

The PRESENT permutation P follows a specific instance of the above lemma, with m=20 and  $i_0=i_1=\cdots=i_{19}=3$ . Thus the fact that

$$P = s_{b_0} \circ s_{b_1} \circ \cdots \circ s_{b_{19}} \circ t_{a_0} \circ t_{a_1} \circ \cdots \circ t_{a_{19}}$$

is a corollary of the above lemma.

## 3.1 Implementation using 2 scan flip-flops

Lemma 2 already states that any permutation in  $S_n$  can be generated by the cycles  $(1,2,\ldots,n)$  and (1,2). In a typical serial implementation, the cycle  $(1,2,\ldots,n)$  naturally appears as the rotation operation of the pipeline, constructed from n flip flops. The swap (1,2) can be realized by simply replacing two of these flip-flops with scan flip-flops. Therefore, Lemma 2 implies the existence of PRESENT permutation realization with only 2 scan flip-flops. Therefore, we explore the number of cycles applying the PRESENT permutation takes, i.e. by deriving the decomposition sequence with a straightforward application of the above formalism.

In order to be compatible with the order of bit addressing used in block ciphers [BKL<sup>+</sup>07, BPP<sup>+</sup>17], we relabel the set of 64 elements by the indices  $\{63, 62, \ldots, 0\}$ . After this relabeling, we can analogously claim that  $S_{64}$  is generated by the cycles w = (62, 63) and  $r = (0, 1, 2, \ldots, 63)$ . The idea is to implement all the transpositions  $t_i$  followed by all the  $s_i$ 's. In order to do so, let us first see how any arbitrary transposition can be implemented only using r and w.

Implementing a transposition (x, y) for (x > y) and  $x, y \in [0, 63]$ : Let  $\overline{x} = 63 - x$ ,  $\overline{y} = 63 - y$ . As per the proofs outlined in Lemmas 1 and 2, we have :

$$\begin{split} (x,y) &= (x,x-1) \circ (x-1,y) \circ (x,x-1) \\ &= (x,x-1) \circ (x-1,x-2) \circ (x-2,y) \circ (x-1,x-2) \circ (x,x-1) \\ &= (x,x-1) \circ (x-1,x-2) \circ \cdots \circ (y+1,y) \circ \cdots \circ (x-1,x-2) \circ (x,x-1) \\ &= (r^{-\overline{x}} \circ w \circ r^{\overline{x}}) \circ (r^{-1-\overline{x}} \circ w \circ r^{1+\overline{x}}) \circ \cdots \circ (r^{1-\overline{y}} \circ w \circ r^{\overline{y}-1}) \circ \cdots \circ \\ &\qquad (r^{-1-\overline{x}} \circ w \circ r^{1+\overline{x}}) \circ (r^{-\overline{x}} \circ w \circ r^{\overline{x}}) \\ &= r^{-\overline{x}} \circ w \circ (r^{-1} \circ w)^{x-y-1} \circ (r \circ w)^{x-y-1} \circ r^{\overline{x}} \\ &= r^{64-\overline{x}} \circ w \circ (r^{63} \circ w)^{x-y-1} \circ (r \circ w)^{x-y-1} \circ r^{\overline{x}} \\ &= r^{1+x} \circ w \circ (r^{63} \circ w)^{x-y-1} \circ (r \circ w)^{x-y-1} \circ r^{63-x} \end{split}$$

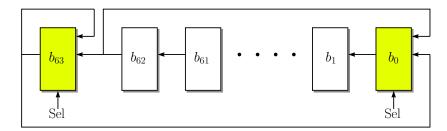

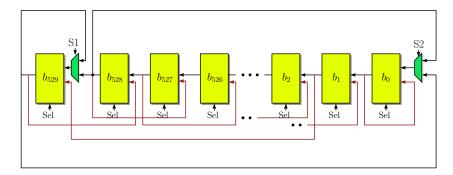

Figure 1: Shift register circuit with (subsequent) 2 scan flip-flops

Given the decomposition (x,y) in terms of r and w as given above, the next question naturally arises as to how to implement it using 2 scan flip-flops. Consider the circuit in Figure 1. It consists of an array of 64 flip-flops, with the 2 at the extreme ends being scan flip-flops controlled by a Sel signal. When Sel is 0, the data in the flip-flops simply rotate bitwise towards the left. When Sel is 1, the  $b_{63}$  bit is held in place, and the data in the remaining 63 flip-flops is rotated left bitwise. Implementing a particular permutation  $\pi \in S_{64}$  on this circuit, essentially tries to answer the following question: If we consider  $b_i(t)$ ,  $i \in [0,63]$ ,  $t \geq 0$  to be the bit value stored on the  $i^{th}$  flip-flop at time t, does there exist some sequence of Sel signals  $s_0, s_1, \ldots, s_{T-1}$  such that for all  $b_0(0), \ldots, b_{63}(0)$ , setting Sel to  $s_t$  at clock cycle t implies that  $b_{\pi(i)}(T) = b_i(0)$  for all t. The length t of the sequence is the number of clock cycles needed to perform the permutation t.

**Lemma 4.** Considering the circuit in Figure 1, implementing an arbitrary swap operation (x, y) requires at most 64(x - y) clock cycles.

*Proof.* To begin with, note that r is a function that performs a rotation operation by one location towards the left. In Figure 1, setting the select signal Sel to 0, causes the shift register to implement the r function, as data follows the circular path marked in the bottom. Setting Sel to 1, brings about the following transformation:

$$(b_{63}, b_{62}, b_{61}, \dots, b_1, b_0) \rightarrow (b_{63}, b_{61}, b_{60}, \dots, b_0, b_{62})$$

This is same as applying the function  $(r \circ w)$ . It is easy to see that r and  $(r \circ w)$  also generate  $S_{64}$ . Thus by controlling the Sel signal, we can make the shift register circuit alternate between r and  $v = (r \circ w)$  functions. Note that (x, y) can be rewritten in blocks of 64 operations each, in the following manner:

$$(x,y) = r^{1+x} \circ w \circ (r^{63} \circ w)^{x-y-1} \circ (r \circ w)^{x-y-1} \circ r^{63-x}$$

$$= [r^x \circ v \circ r^{63-x}] \circ [r^{x-1} \circ v \circ r^{64-x}] \circ \dots \circ [r^{y+2} \circ v \circ r^{61-y}] \circ [r^{y+1} \circ v^{x-y} \circ r^{63-x}]$$

Each block of operations in square braces in the above equation is a set of 64 operations, and thus would take 64 clock cycles to execute using the shift register circuit. Since there are a total of (x - y) braces, the result follows.

**Corollary 1.** Employing the shift register circuit in figure 1, one round of the PRESENT bit permutation can be executed in 36480 clock cycles.

*Proof.* The idea is to execute the PRESENT permutation P by executing each of the transpositions  $t_i$  and then  $s_i$  sequentially. Denoting  $t_i = (x_i, y_i)$  and  $s_i = (x_{20+i}, y_{20+i})$  for  $i \in [0, 19]$ , (with  $x_i > y_i$ ) the number of clock cycles can be calculated as  $\sum_{i=0}^{39} 64 \cdot (x_i - y_i) = 36480$ .

This result is a pessimistic one since it implies that to perform the PRESENT encryption operation on a shift register based circuit as given in Figure 1, would result in heavy loss of throughput. In the following subsections, we will try to see if the number of operations can be reduced in any way.

## 3.2 Decreasing the number of operations

Before we outline the method used to reduce the number of operations, let us look at the following definition.

**Definition 1.** As in Lemma 4, let  $\pi$  be a permutation in  $S_n$  whose disjoint cycle decomposition consists of the cycles  $c_0, c_1, \ldots, c_{m-1}$  each with orders  $i_0, i_1, \ldots, i_{m-1}$  respectively. Let each  $c_j$  be expressed as composition of  $i_j - 1$  transpositions  $s_j(1), s_j(2), \ldots, s_j(i_j - 1)$ . Denote the transposition  $s_j(k) = (x_j(k), y_j(k))$  with  $x_j(k) > y_j(k)$ .  $\pi$  is said to be a special permutation of the type  $\kappa$ , if  $\kappa$  is the largest integer for which the following holds:

$$x_j(k) - y_j(k) \equiv 0 \mod \kappa, \quad \forall j \in [0, m-1], \forall k \in [0, i_j - 1]$$

It is easy to see from Table 2, that the PRESENT permutation P is a special permutation of type 3. Before we proceed, let us look at a result concerning special permutations of type  $\kappa$ .

**Lemma 5.** Let  $G_{\kappa}$  denote the set of all the special permutations of  $S_{64}$  of type  $\kappa$ . Then  $G_{\kappa}$  can be generated by the permutations  $w_{\kappa} = (63 - \kappa, 63)$  and  $r = (0, 1, \dots, 63)$ .

*Proof.* The only thing we need to show is that any transposition (x, y) with x > y and  $x \equiv y \mod \kappa$ , can be generated using  $w_{\kappa}$  and r. Let  $z = \frac{x-y}{\kappa}$ . We have

$$\begin{split} (x,y) &= (x,x-\kappa) \circ (x-\kappa,y) \circ (x,x-\kappa) \\ &= (x,x-\kappa) \circ (x-\kappa,x-2\kappa) \circ (x-2\kappa,y) \circ (x-\kappa,x-2\kappa) \circ (x,x-\kappa) \\ &= (x,x-\kappa) \circ (x-\kappa,x-2\kappa) \circ \cdots \circ (y+\kappa,y) \circ \cdots \circ (x-\kappa,x-2\kappa) \circ (x,x-\kappa) \\ &= (r^{-\overline{x}} \circ w_{\kappa} \circ r^{\overline{x}}) \circ (r^{-\kappa-\overline{x}} \circ w_{\kappa} \circ r^{\kappa+\overline{x}}) \circ \cdots \circ (r^{\kappa-\overline{y}} \circ w_{\kappa} \circ r^{\overline{y}-\kappa}) \circ \cdots \circ \\ &\quad (r^{-\kappa-\overline{x}} \circ w_{\kappa} \circ r^{\kappa+\overline{x}}) \circ (r^{-\overline{x}} \circ w_{\kappa} \circ r^{\overline{x}}) \\ &= r^{-\overline{x}} \circ w_{\kappa} \circ (r^{-\kappa} \circ w_{\kappa})^{z-1} \circ (r^{\kappa} \circ w_{\kappa})^{z-1} \circ r^{\overline{x}} \\ &= r^{64-\overline{x}} \circ w_{\kappa} \circ (r^{64-\kappa} \circ w_{\kappa})^{z-1} \circ (r^{\kappa} \circ w_{\kappa})^{z-1} \circ r^{\overline{x}} \\ &= r^{1+x} \circ w_{\kappa} \circ (r^{64-\kappa} \circ w_{\kappa})^{z-1} \circ (r^{\kappa} \circ w_{\kappa})^{z-1} \circ r^{63-x} \end{split}$$

The next step naturally is too see how any transposition (x,y) with  $x \equiv y \mod \kappa$  can be implemented in a shift register structure using only 2 scan flip-flops using a method that requires lesser number of cycles as compared to the previous construction. We try to address this is the next lemma.

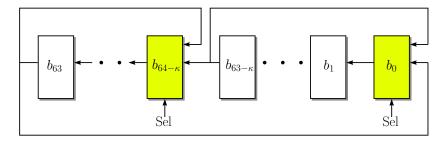

**Lemma 6.** Consider the circuit in Figure 2. Implementing an arbitrary swap operation (x,y) with x > y and  $x \equiv y \mod \kappa$  using it can be implemented in  $\frac{64(x-y)}{\kappa} = 64z$  clock cycles.

*Proof.* As before, setting Sel to 0, executes the rotate function r. Setting Sel to 1, achieves the following transformation:

$$(b_{63}, b_{62}, b_{61}, \dots, b_1, b_0) \rightarrow (b_{62}, b_{61}, \dots, b_{64-\kappa}, b_{63}, b_{62-\kappa}, b_{61-\kappa}, \dots, b_0, b_{63-\kappa})$$

Figure 2: Shift register circuit with ( $\kappa$ -respecting) 2 scan flip-flops

This is same as applying the transformation  $v_{\kappa} = r \circ w_{\kappa}$ . Thus, as before, controlling Sel makes the circuit alternate between r and  $v_{\kappa}$  operations. As before we express (x, y) in blocks of 64 operations:

$$\begin{split} (x,y) &= r^{1+x} \circ w_{\kappa} \circ (r^{64-\kappa} \circ w_{\kappa})^{z-1} \circ (r^{\kappa} \circ w_{\kappa})^{z-1} \circ r^{63-x} \\ &= [r^{x} \circ v_{\kappa} \circ r^{63-x}] \circ [r^{x-\kappa} \circ v_{\kappa} \circ r^{63-x+\kappa}] \circ \cdots \circ [r^{x-(z-2)\kappa} \circ v_{\kappa} \circ r^{63-x+(z-2)\kappa}] \circ \\ & [r^{y+1} \circ (r^{\kappa-1} \circ v_{\kappa})^{z} \circ r^{63-x}] \end{split}$$

Operations in each of the square braces take 64 cycles and since there are exactly z such braces, the result follows.

**Corollary 2.** Using the shift register circuit in Figure 2, one round of the PRESENT bit permutation P can be executed in 12160 clock cycles.

*Proof.* We have already noted that P is a special permutation of type 3. As in the previous corollary, let  $t_i = (x_i, y_i)$  and  $s_i = (x_{20+i}, y_{20+i})$  for  $i \in [0, 19]$ , (with  $x_i > y_i$ ). For performing all the  $t_i$ 's followed by all the  $s_i$ 's sequentially, the number of clock cycles can be calculated as  $\sum_{i=0}^{39} 64 \cdot \frac{(x_i - y_i)}{3} = 12160$ .

By using the modified shift register structure, we obtain a threefold increase of throughput in computation of the PRESENT permutation. However, this is still way too slow, and in the subsequent sections we will try to find if the computations can be further sped up.

## 3.3 Further reduction

Until so far, we were executing each transposition operation sequentially, i.e. one after the other. However in the interest of speeding up computations, let us investigate if it is at all possible to execute some of the swap operations concurrently.

**Definition 2.** Define Let  $\sigma=(x,y)$  be a transposition in  $S_{64}$  with x>y.  $\overrightarrow{\mathsf{Sel}}_{\sigma}$  to be the vector of  $\overrightarrow{\mathsf{Sel}}_{\sigma}$  is therefore  $\frac{64(x-y)}{\kappa}$ . For example, let  $\kappa=3$ , as in PRESENT. Consider  $\sigma=(60,51)$ , for which z=3. We have

$$\begin{split} \sigma &= [r^x \circ v_\kappa \circ r^{63-x}] \circ [r^{x-\kappa} \circ v_\kappa \circ r^{63-x+\kappa}] \circ \cdots \circ [r^{x-(z-2)\kappa} \circ v_\kappa \circ r^{63-x+(z-2)\kappa}] \circ \\ &\quad [r^{y+1} \circ (r^{\kappa-1} \circ v_\kappa)^z \circ r^{63-x}] \\ &= [r^{60} \circ v_3 \circ r^3] \circ [r^{57} \circ v_3 \circ r^6] \circ [r^{52} \circ (r^2 \circ v_3)^3 \circ r^3] \\ \overrightarrow{\operatorname{Sel}}_{\sigma} &= \underbrace{0^{60} \ 1 \ 0^3 \quad 0^{57} \ 1 \ 0^6 \quad 0^{52} \ 0^2 1 \ 0^2 1 \ 0^3}_{\leftarrow \quad \operatorname{Increasing Index}} \end{split}$$

Note that to keep notations consistent as to the order of application of the permutations, the rightmost element in the vector is denoted as the  $0^{th}$  element, and the index is increased as we go left. This is consistent with the order of application in the composition notation, in which the rightmost permutation of the composition is applied first. Let us now re-write the permutations r and  $v_{\kappa}$  in functional form:

$$r(\alpha) = (\alpha+1) \bmod 64, \quad v_{\kappa}(\alpha) = \left\{ \begin{array}{ll} 64 - \kappa, & \text{if } \alpha = 63, \\ 0, & \text{if } \alpha = 63 - \kappa, \\ (\alpha+1) \bmod 64, & \text{otherwise.} \end{array} \right.$$

We can see that r and  $v_{\kappa}$  differ on only two inputs 63 and 63  $-\kappa$ . By stretching notations slightly, let  $\overrightarrow{\mathsf{Sel}}_p$  also denote a random 64 bit binary vector that implements the permutation p when fed to the  $\mathsf{Sel}$  port of the circuit in Figure 2 over 64 consecutive clock cycles. Let  $\mathbb{B}_p$  be the set of elements that denote the positions of 1's in  $\overrightarrow{\mathsf{Sel}}_p$ . From the functional equations of r and  $v_{\kappa}$ , it is not difficult to deduce that (a simple code in programming language is sufficient to do this)  $\mathbb{A}_p = \mathbb{U}_p \cup \mathbb{V}_p$ , where

$$\mathbb{U}_p = \{63 - \alpha : \alpha \in \mathbb{B}_p\}, \ \mathbb{V}_p = \{63 - \alpha - \kappa \bmod 64 : \alpha \in \mathbb{B}_p\}$$

It is also possible to deduce p from  $\mathbb{B}_p$ . If  $\mathbb{B}_p$  contains elements  $b, b+\kappa, b+2\kappa, \ldots, b+(l-1)\kappa$  which are in an arithmetic sequence with common difference  $\kappa$  then we will have

$$p(63 - b - i\kappa) = 63 - b - (i - 1)\kappa, \ \forall i \in [1, l], \ \text{and} \ \ p(63 - b) = 63 - b - l\kappa$$

For all other elements  $\hat{b}$  in  $\mathbb{B}_p$  that are not part of an arithmetic sequence with common difference  $\kappa$ , we have  $p(63 - \hat{b}) = 63 - \hat{b} - \kappa$  and  $p(63 - \hat{b} - \kappa) = 63 - \hat{b}$ . For all other elements we have p(b) = b.

**Example 1.** For example if  $\mathbb{B}_p = \{6, 9, 19, 29, 53, 56, 60, 61\}$  with  $\kappa = 3$ , we see that we have 2 arithmetic sequences of common difference 3: 6, 9 and 53, 56. So we have  $\mathbb{A}_p = \{0, 2, 3, 4, 7, 10, 31, 34, 41, 44, 51, 54, 57, 63\}$  We have  $p = (51, 54, 57) \circ (4, 7, 10) \circ (44, 41) \circ (34, 31) \circ (3, 0) \circ (2, 63)$ .

Consider every 64 bit block of the  $\overrightarrow{\mathsf{Sel}}_\sigma$  vector. Let  $\pi_i$  (for i=0 to z-1) be the composition of all the permutations in the  $i^{th}$  64-bit block. Let us use the notation

$$\overrightarrow{\mathsf{Sel}}_{\sigma} = \overrightarrow{\mathsf{Sel}}_{\pi_{z-1}} || \overrightarrow{\mathsf{Sel}}_{\pi_{z-2}} || \cdots || \overrightarrow{\mathsf{Sel}}_{\pi_{2}} || \overrightarrow{\mathsf{Sel}}_{\pi_{1}} || \overrightarrow{\mathsf{Sel}}_{\pi_{0}}.$$

Of course we have  $\sigma = \pi_{z-1} \circ \pi_{z-2} \circ \cdots \circ \pi_2 \circ \pi_1 \circ \pi_0$ . In the above example, for  $\sigma = (60, 51)$  we have  $\mathbb{B}_{\pi_0} = \{3, 6, 9\}$ ,  $\mathbb{B}_{\pi_1} = \{6\}$ ,  $\mathbb{B}_{\pi_2} = \{3\}$ . Generalizing the above we can see that  $\mathbb{B}_{\pi_0} = \{63 - x, 63 - x - \kappa, \dots, 63 - y - \kappa\}$ .  $\mathbb{B}_{\pi_0}$  only contains elements that are  $\overline{x} = 63 - x \mod \kappa$ . And we have that  $\mathbb{B}_{\pi_i} \subset \mathbb{B}_{\pi_0}$ ,  $\forall i > 0$ . From the analysis presented above, it can be deduced that for all i,

$$\pi_i(\alpha) = \alpha, \ \forall \alpha \not\equiv x \bmod \kappa.$$

This is because the 1's (equivalently  $v_{\kappa}$ 's) in this block appear at distances of  $\kappa$ . If we apply each function in  $\pi_i$  one by one, for any input  $\alpha \not\equiv x \mod \kappa$ , the corresponding input to  $v_{\kappa}$  is never 63 or 63  $-\kappa$ , and so a plain rotation is effectively executed. Therefore all the  $\pi_i$ 's perform shuffling on only a subset of elements that are congruent to  $x \mod \kappa$  and leave the others untouched. From the equation  $\mathbb{A}_p = \mathbb{U}_p \cup \mathbb{V}_p$ , we can also deduce that  $\mathbb{A}_{\pi_0} = \{x, x - \kappa, x - 2\kappa, \dots, y\}$ . Thus each  $\pi_i$  is effectively a permutation function on only a subset of  $\{0, 1, 2, 3, \dots, 63\}$  that are congruent to  $x \mod \kappa$  and effectively follows the transition shown in Figure 3.

$$\pi_{0}: \qquad x, x - \kappa, x - 2\kappa, \dots, y + 2\kappa, y + \kappa, y \longrightarrow x - \kappa, x - 2\kappa, \dots, y + 2\kappa, y + \kappa, y, x$$

$$\pi_{1}: \qquad x - \kappa, x - 2\kappa, \dots, y + 2\kappa, y + \kappa, y, x \longrightarrow x - \kappa, x - 2\kappa, \dots, y + 2\kappa, y + \kappa, x$$

$$\pi_{2}: \qquad x - \kappa, x - 2\kappa, \dots, y + 2\kappa, y, y + \kappa, x \longrightarrow x - \kappa, x - 2\kappa, \dots, y, y + 2\kappa, y + \kappa, x$$

$$\vdots$$

$$\vdots$$

$$\pi_{z-1}: \qquad x - \kappa, y, \dots, y + 3\kappa, y + 2\kappa, y + \kappa, x \longrightarrow y, x - \kappa, x - 2\kappa, \dots, y + 2\kappa, y + \kappa, x$$

Figure 3: Rotations in each  $\pi_i$

Figure 3 provides more insights into the working of each  $\pi_i$ .  $\pi_0$  effectively rotates the elements in the set  $\{x, x - \kappa, x - 2\kappa, \dots, y\}$  by one location to the left, and delivers x to location y. The other  $\pi_i$ 's are mini-swaps, that lets y bubble up to position x after z - 1 executions. From the figure we can see that  $\mathbb{A}_{\pi_1 \circ \pi_0} = \mathbb{A}_{\pi_0} - \{y + \kappa\}$  and more generally,  $\mathbb{A}_{\pi_i \circ \dots \circ \pi_0} = \mathbb{A}_{\pi_{i-1} \circ \dots \circ \pi_0} - \{y + i\kappa\}$ .

**Lemma 7.** Let  $\overrightarrow{\mathsf{Sel}}_{p_1}$  and  $\overrightarrow{\mathsf{Sel}}_{p_2}$  be two 64 bit signal vectors implementing permutations  $p_1$  and  $p_2$  on the circuit of Figure 2. If  $\mathbb{A}_{p_1} \cap \mathbb{A}_{p_2} = \varnothing$ , then  $p_1 \circ p_2$  can be concurrently executed on this circuit using the signal vector  $\overrightarrow{\mathsf{Sel}}_{p_1} \upharpoonright \overrightarrow{\mathsf{Sel}}_{p_2}$ , where  $\upharpoonright$  denotes a bitwise OR operation on the vectors.

Proof. See Appendix B.

$$\Box$$

**Lemma 8.** Let  $\sigma_1 = (x_1, y_1)$  and  $\sigma_2 = (x_2, y_2)$  be two special transpositions  $(x_i > y_i, i = 1, 2)$  in  $S_{64}$  of type  $\kappa$ . Without loss of generality let  $\ell_1 = (x_1 - y_1) \ge (x_2 - y_2) = \ell_2$ , and  $z_i = \frac{\ell_i}{\kappa}$ . Let the respective decompositions are denoted by the symbols  $\pi_i$  and  $\theta_i$ , i.e.  $\sigma_1 = \pi_{z_1-1} \circ \pi_{z_1-2} \circ \cdots \circ \pi_2 \circ \pi_1 \circ \pi_0$  and  $\sigma_2 = \theta_{z_2-1} \circ \theta_{z_2-2} \circ \cdots \circ \theta_2 \circ \theta_1 \circ \theta_0$ . Sel  $\sigma_1$  and Sel  $\sigma_2$  may not be of the same length, in which case append  $\sigma_1$  appears to Sel  $\sigma_2$  to make them of the same length. If  $\sigma_1 \cap \sigma_2 \cap \sigma_1$  to the same length in Figure 2 and achieve  $\sigma_1 \circ \sigma_2 \cap \sigma_2$  in  $\sigma_2 \cap \sigma_3 \cap \sigma_4$  and  $\sigma_3 \cap \sigma_4 \cap \sigma_5$  be the vector of Sel signals required to achieve this. Then  $\sigma_3 \cap \sigma_4 \cap \sigma_5 \cap \sigma_6$  in  $\sigma_4 \cap \sigma_5 \cap \sigma_6$  and  $\sigma_5 \cap \sigma_6 \cap \sigma_6$  be the vector of Sel signals required to achieve this. Then  $\sigma_3 \cap \sigma_4 \cap \sigma_5 \cap \sigma_6$  in  $\sigma_4 \cap \sigma_6 \cap \sigma_6$  in  $\sigma_5 \cap \sigma_6 \cap \sigma_6$  and  $\sigma_6 \cap \sigma_6 \cap \sigma_6$  in  $\sigma_6 \cap \sigma_6$

*Proof.* See Appendix C.

$$\Box$$

The above result may be extended to a set of any number of special transpositions  $\sigma_i$  (i=1 to k) of the type  $\kappa$ , provided that the respective  $\mathbb{A}_{\pi_0}$  sets are pairwise disjoint. In that case we have

$$\overrightarrow{\mathsf{Sel}}_{\sigma_1 \circ \sigma_2 \circ \cdots \circ \sigma_k} = \overrightarrow{\mathsf{Sel}}_{\sigma_1} \widehat{|} \ \overrightarrow{\mathsf{Sel}}_{\sigma_2} \widehat{|} \ \cdots \widehat{|} \ \overrightarrow{\mathsf{Sel}}_{\sigma_k}$$

Corollary 3. Let  $\sigma_1 = (x_1, y_1)$  and  $\sigma_2 = (x_2, y_2)$  be two transpositions  $(x_i > y_i, i = 1, 2)$  in  $S_{64}$  such that  $x_1 - y_1 \equiv x_2 - y_2 \mod \kappa$ , and  $x_1 \not\equiv x_2 \mod \kappa$ . Without loss of generality let  $\ell_1 = (x_1 - y_1) \ge (x_2 - y_2) = \ell_2$ , and  $z_i = \frac{\ell_i}{\kappa}$ . As before, let the respective decompositions are denoted by the symbols  $\pi_i$  and  $\theta_i$  and append  $64(z_1 - z_2)$  zeroes to  $\overrightarrow{\mathsf{Sel}}_{\sigma_2}$  to make the two  $\overrightarrow{\mathsf{Sel}}$  vectors of the same length. It is possible to execute  $\sigma_1$  and  $\sigma_2$  concurrently on the circuit in Figure 2 and achieve  $\sigma_1 \circ \sigma_2$  in  $64 \cdot z_1$  clock cycles by using  $\overrightarrow{\mathsf{Sel}}_{\sigma_1} \upharpoonright \overrightarrow{\mathsf{Sel}}_{\sigma_2}$  as the select signal vector.

$<sup>^{1}</sup>$ Since  $r^{64}$  is the identity function, this does not affect either permutation

*Proof.* We have already seen that for any transposition  $\sigma = (x, y) = \pi_{z-1} \circ \cdots \circ \pi_0$ , we have  $\mathbb{A}_{\pi_0} = \{x, x - \kappa, x - 2\kappa, \dots, y\}$ . Thus  $\mathbb{A}_{\pi_0}$  contains elements that are only congruent to  $x \mod \kappa$ . Since  $x_1, y_1$  and  $x_2, y_2$  belong to different equivalence classes modulo  $\kappa$ ,  $\mathbb{A}_{\pi_0} \cap \mathbb{A}_{\theta_0} = \emptyset$ . Thus the result follows.  $\square$

Corollary 4. Let  $\sigma_1 = (x_1, y_1)$  and  $\sigma_2 = (x_2, y_2)$  be two transpositions  $(x_i > y_i, i = 1, 2)$  in  $S_{64}$  such that  $y_1 > x_2$ . Let  $\ell_1 = (x_1 - y_1) \ge (x_2 - y_2) = \ell_2$ , and  $z_i = \frac{\ell_i}{\kappa}$ . Let the respective decompositions are denoted by the symbols  $\pi_i$  and  $\theta_i$ . Then after making the Sel vectors of the same length by appending zeroes, it is possible to execute  $\sigma_1$  and  $\sigma_2$  concurrently on the circuit in Figure 2 and achieve  $\sigma_1 \circ \sigma_2$  in  $64 \cdot z_1$  clock cycles by using  $\overrightarrow{\text{Sel}}_{\sigma_1} \upharpoonright \overrightarrow{\text{Sel}}_{\sigma_2}$  as the select signal vector.

*Proof.* We have

$$\mathbb{A}_{\pi_0} = \{x_1, x_1 - \kappa, x_1 - 2\kappa, \dots, y_1\}$$

and  $\mathbb{A}_{\theta_0} = \{x_2, x_2 - \kappa, x_2 - 2\kappa, \dots, y_2\}$ . Since  $y_1 > x_2$ , clearly  $\mathbb{A}_{\pi_0} \cap \mathbb{A}_{\theta_0} = \emptyset$ . Thus the result follows.  $\square$

We can use the results in the above two corollaries to further reduce the execution time of the PRESENT permutation. We have to execute all the transpositions  $t_i$  followed by the transpositions  $s_i$ . The idea is to execute as many permutations concurrently which have pairwise disjoint  $\mathbb{A}_{\pi_0}$ 's. We can easily partition the transpositions modulo  $\kappa=3$ . Transpositions that are in different classes modulo 3 can obviously be executed concurrently. Also transpositions in the same class modulo 3, which have disjoint  $\mathbb{A}_{\pi_0}$ 's can also be executed together. For the  $t_i$ 's we can think of the following solution given in Table 4, that takes  $(11+7+1)\cdot 64=704+448+64=1216$  cycles. All the swaps in  $i^{th}$  group can be executed concurrently, thereby reducing the number of cycles.

| Group | mod3 | $ig  t_i$                 | $\max(x_i - y_i)$ | #Cycles |

|-------|------|---------------------------|-------------------|---------|

| 1     | 0    | (57,39), (36,18), (12,3)  | 33                | 704     |

|       | 1    | (61,55), (52,19), (4,1)   |                   |         |

|       | 2    | (62,59), (44,11), (8,2)   |                   |         |

| 2     | 0    | (60,51), (45,27), (24,6)  | 21                | 448     |

|       | 1    | (46,43), (40,34), (28,7)  |                   |         |

|       | 2    | (56,35), (29,23), (20,17) |                   |         |

| 3     | 1    | (25, 22)                  | 3                 | 64      |

|       | 2    | (41, 38)                  |                   |         |

Table 3: Concurrent execution of the  $t_i$ 's in the PRESENT permutation

A similar construction for the  $s_i$ 's will take  $(12+12+7+4)\cdot 64=2240$  cycles. So a total of 1216+2240=3456 cycles are required which is already way better than our previous construction of 12160 cycles.

## 3.4 Final Optimization

In this final subsection we see if the number of clock cycles can be further optimized. Specifically we want to see if it is possible to implement transpositions  $\sigma_1$  and  $\sigma_2$  concurrently, even if the corresponding  $\mathbb{A}_{\pi_0} \cap \mathbb{A}_{\theta_0} \neq \emptyset$ . We start with a well known result in permutation theory.

**Theorem 1.** For every permutation  $\sigma \in S_{64}$ , and every transposition  $(x,y) \in S_{64}$ :

$$f = \sigma \circ (x, y) = (\sigma(x), \sigma(y)) \circ \sigma$$

| Group | mod3 | $s_i$                    | $\max(x_i - y_i)$ | #Cycles |

|-------|------|--------------------------|-------------------|---------|

| 1     | 0    | (51, 15)                 | 36                | 768     |

|       | 1    | (55,31), (19,13)         |                   |         |

|       | 2    | (53,29), (17,5)          |                   |         |

| 2     | 0    | (48, 12)                 | 36                | 768     |

|       | 1    | (58,46), (34,10)         |                   |         |

|       | 2    | (59,47), (32,8)          |                   |         |

| 3     | 0    | (54,45), (39,30), (18,9) | 21                | 448     |

|       | 1    | (49,28), (16,4)          |                   |         |

|       | 2    | (50,44), (35,14)         |                   |         |

| 4     | 0    | (33, 24)                 | 12                | 256     |

|       | 1    | (37, 25)                 |                   |         |

|       | 2    | (38, 26)                 |                   |         |

Table 4: Concurrent execution of the  $s_i$ 's in the PRESENT permutation

The above is not difficult to prove,  $\forall \alpha \notin \{x, y\}$ , we have  $f(\alpha) = \sigma(\alpha)$ . And both sides evaluates to  $f(x) = \sigma(y)$  and  $f(y) = \sigma(x)$ .

**Lemma 9.** Let  $\sigma_1 = (x_1, y_1)$  and  $\sigma_2 = (x_2, y_2)$  be two special disjoint transpositions  $(x_i > y_i, i = 1, 2)$  in  $S_{64}$  of type  $\kappa$ . Without loss of generality let  $\ell_1 = (x_1 - y_1) \ge (x_2 - y_2) = \ell_2$ , and  $z_i = \frac{\ell_i}{\kappa}$ . Let the respective decompositions are denoted by the symbols  $\pi_i$  and  $\theta_i$ , i.e.  $\sigma_1 = \pi_{z_1-1} \circ \pi_{z_1-2} \circ \cdots \circ \pi_2 \circ \pi_1 \circ \pi_0$  and  $\sigma_2 = \theta_{z_2-1} \circ \theta_{z_2-2} \circ \cdots \circ \theta_2 \circ \theta_1 \circ \theta_0$ . Let us have  $A_{\pi_0} \cap A_{\theta_0} \neq \emptyset$ . Denote by  $P = (\pi[i \to 0](x_2), \pi[i \to 0](y_2))$ , for some  $i \in [0, z_1 - 1]$ . Let the decomposition of P be denoted as

$$p = \gamma_{q-1} \circ \gamma_{q-2} \circ \cdots \circ \gamma_1 \circ \gamma_0.$$

Now denote  $\overrightarrow{\mathsf{Sel}}_1 = \overrightarrow{\mathsf{Sel}}_{\pi_{z_1-1}} || \overrightarrow{\mathsf{Sel}}_{\pi_{z_1-2}} || \cdots || \overrightarrow{\mathsf{Sel}}_{\pi_{i+1}} \text{ and } \overrightarrow{\mathsf{Sel}}_2 = \overrightarrow{\mathsf{Sel}}_p$ . After appending with zeroes to make  $\overrightarrow{\mathsf{Sel}}_1$  and  $\overrightarrow{\mathsf{Sel}}_2$  of the same length, the following vector

$$\overrightarrow{\mathsf{Sel}}_1 \hat{|} \overrightarrow{\mathsf{Sel}}_2 \mid | \overrightarrow{\mathsf{Sel}}_{\pi[i \to 0]}$$

will execute  $\sigma_1 \circ \sigma_2$  on the circuit in Figure 2, if  $\mathbb{B}_{\gamma_0} \cap \mathbb{B}_{\pi_{i+1}} = \emptyset$ .

*Proof.* See Appendix D.

**Example 2.** An immediate application of the above is to construct a  $\overrightarrow{\mathsf{Sel}}$  vector to execute (51,15) and (48,12) concurrently on the PRESENT circuit. In the previous subsection we had executed them sequentially which had cost us  $12 \cdot 64 = 768$  cycles each. Start with  $\sigma_1 = (48,12)$ . We have  $\mathbb{B}_{\pi_0} = \{15,18,21,24,27,30,33,36,39,42,45,48\}$ ,  $\mathbb{B}_{\pi_j} = \{48-3j\}$  for  $1 \leq j \leq 11$ . For  $\sigma_2 = (51,15)$ , we observe that  $(\pi_0(51),\pi_0(15)) = (51,18)$ . If we let p = (51,18), then  $\mathbb{B}_{\gamma_0} = \{12,15,18,21,24,27,30,33,36,39,42\}$ . Since  $\mathbb{B}_{\gamma_0} \cap \mathbb{B}_{\pi_1} = \varnothing$ , this choice of p will work. Also  $\overrightarrow{\mathsf{Sel}}_1$  and  $\overrightarrow{\mathsf{Sel}}_2$  will be of the same length, due to which zero padding is also not required. So we have  $\mathbb{B}_{\gamma_j} = \{42-3j\}$  for all  $1 \leq j \leq 10$ . Since  $\overrightarrow{\mathsf{Sel}}_{\sigma_1 \circ \sigma_2} = \overrightarrow{\mathsf{Sel}}_1 \upharpoonright \overrightarrow{\mathsf{Sel}}_2 \mid \mid \overrightarrow{\mathsf{Sel}}_{\pi[i \to 0]}$ , denoting the decomposition of  $\sigma_1 \circ \sigma_2$  by the symbols  $\eta_j$ , we have  $\mathbb{B}_{\eta_0} = \mathbb{B}_{\pi_0}$ ,  $\mathbb{B}_{\eta_{j+1}} = \mathbb{B}_{\pi_{j+1}} \cup \mathbb{B}_{\gamma_j}$  for  $0 \leq j \leq 10$ . This therefore implements  $\sigma_1 \circ \sigma_2$  in only  $12 \cdot 64 = 768$  cycles.

In the next lemma, we take things forward. If  $\sigma$  is a permutation which implements a set of disjoint transpositions (instead of just a single transposition), it may be possible to implement another transposition  $\sigma'$  concurrently along with  $\sigma$  if certain conditions are met

**Lemma 10.** Let  $\sigma$  be a special permutation of type  $\kappa$  that is a composition of several pairwise disjoint transpositions. Let  $\sigma' = (x, y)$  be a special transposition (x > y) of type  $\kappa$ , that is also pairwise disjoint with each of the transpositions that compose  $\sigma$ . Let the respective decompositions are denoted by the symbols  $\pi_i$  and  $\theta_i$ , i.e.  $\sigma = \pi_{z_1-1} \circ \pi_{z_1-2} \circ \cdots \circ \pi_2 \circ \pi_1 \circ \pi_0$  and  $\sigma' = \theta_{z_2-1} \circ \theta_{z_2-2} \circ \cdots \circ \theta_2 \circ \theta_1 \circ \theta_0$ . Let us have  $\mathbb{A}_{\pi_0} \cap \mathbb{A}_{\theta_0} \neq \emptyset$ . Denote by  $p = (\pi[i \to 0](x), \pi[i \to 0](y))$ , for some  $i \in [0, z_1 - 1]$ . Let the decomposition of p be denoted as

$$p = \gamma_{q-1} \circ \gamma_{q-2} \circ \cdots \circ \gamma_1 \circ \gamma_0.$$

Now denote  $\overrightarrow{\mathsf{Sel}}_1 = \overrightarrow{\mathsf{Sel}}_{\pi_{z_1-1}} || \overrightarrow{\mathsf{Sel}}_{\pi_{z_1-2}} || \cdots || \overrightarrow{\mathsf{Sel}}_{\pi_{i+1}} \text{ and } \overrightarrow{\mathsf{Sel}}_2 = \overrightarrow{\mathsf{Sel}}_p$ . After appending with zeroes to make  $\overrightarrow{\mathsf{Sel}}_1$  and  $\overrightarrow{\mathsf{Sel}}_2$  of the same length, the following vector

$$\overrightarrow{\mathsf{Sel}}_1 \widehat{\mid} \overrightarrow{\mathsf{Sel}}_2 \mid | \overrightarrow{\mathsf{Sel}}_{\pi[i \to 0]}$$

will execute  $\sigma \circ \sigma'$  on the circuit in Figure 2, if  $\mathbb{B}_{\gamma_0} \cap \mathbb{B}_{\pi_{i+1}} = \varnothing$ .

*Proof.* We give a sketch of the proof as a complete analytical proof is likely to be quite complicated. The idea is similar to the ideas explained in the proof of Lemma 9. Note that  $\mathbb{B}_{\pi_{i+j+1}}$   $(j \geq 0)$  will be the union of the corresponding  $\mathbb{B}$  sets of the several transpositions that compose  $\sigma$ . One has to iterate the "disjoincy" arguments introduced in Lemma 9, for  $\mathbb{B}_{\gamma_0}$  and each of those  $\mathbb{B}$  sets to arrive at a proof.

**Example 3.** Let us construct a  $\overrightarrow{Sel}$  vector for all the  $s_i$ 's in PRESENT that are congruent to 0 mod 3. The transpositions are (51,15), (48,12), (54,45), (39,30), (18,9), (33,24). We already have a  $\overrightarrow{Sel}$  vector for  $(51,15) \circ (48,12)$  in the previous example.

- 1. To start, we have  $\sigma = (51, 15) \circ (48, 12)$ ,  $\mathbb{B}_{\pi_0} = \{15, 18, 21, 24, 27, 30, 33, 36, 39, 42, 45, 48\}$ ,  $\mathbb{B}_{\pi_1} = \{12, 15, 18, 21, 24, 27, 30, 33, 36, 39, 42, 45\}$ , and  $\mathbb{B}_{\pi_j} = \{48 3j, 45 3j\}$  for all  $2 \le j \le 11$ . Let  $\sigma' = (54, 45)$ . Now  $(\pi[1 \to 0](54), \pi[1 \to 0](45)) = (54, 51)$ . If p = (54, 51) then  $\mathbb{B}_{\gamma_0} = \{9\}$ . which is disjoint with  $\mathbb{B}_{\pi_2} = \{42, 39\}$ . Since  $\mathbb{B}_{\gamma_0}$  has only one element it is sufficient to generate p. So we have  $\mathbb{B}_{\eta_2} = \mathbb{B}_{\pi_2} \cup \mathbb{B}_{\gamma_0} = \{42, 39, 9\}$ . For all other j, we have  $\mathbb{B}_{\eta_j} = \mathbb{B}_{\pi_j}$ . This will give us  $\sigma \circ \sigma'$ .

- 2. This time  $\sigma = (51,15) \circ (48,12) \circ (54,45)$ . Shifting notations, we have  $\mathbb{B}_{\pi_0} = \{15,18,21,24,27,30,33,36,39,42,45,48\}$ ,  $\mathbb{B}_{\pi_1} = \{12,15,18,21,24,27,30,33,36,39,42,45\}$ ,  $\mathbb{B}_{\pi_2} = \{42,39,9\}$ , and  $\mathbb{B}_{\pi_j} = \{48-3j,45-3j\}$  for all  $3 \leq j \leq 11$ . Let  $\sigma' = (33,24)$ . Now  $(\pi[1 \to 0](33), \pi[1 \to 0](24)) = (39,30)$ . If p = (39,30) then  $\mathbb{B}_{\gamma_0} = \{24,27,30\}$ . which is disjoint with  $\mathbb{B}_{\pi_2} = \{42,39,9\}$ . We have  $\mathbb{B}_{\gamma_1} = \{27\}$  and  $\mathbb{B}_{\gamma_2} = \{24\}$ . So we have  $\mathbb{B}_{\eta_2} = \mathbb{B}_{\pi_2} \cup \mathbb{B}_{\gamma_0} = \{42,39,30,27,24,9\}$ ,  $\mathbb{B}_{\eta_3} = \mathbb{B}_{\pi_3} \cup \mathbb{B}_{\gamma_1} = \{39,36,27\}$ ,  $\mathbb{B}_{\eta_4} = \mathbb{B}_{\pi_4} \cup \mathbb{B}_{\gamma_2} = \{36,33,24\}$ . For all other j, we have  $\mathbb{B}_{\eta_j} = \mathbb{B}_{\pi_j}$ .

- 3. Now  $\sigma = (51, 15) \circ (48, 12) \circ (54, 45) \circ (33, 24)$ . Since we are using shifting notations, all  $\mathbb{B}_{\pi_j}$ 's are the corresponding  $\mathbb{B}_{\eta_j}$ 's of the previous iteration. Let  $\sigma' = (39, 30)$ . Now  $(\pi[2 \to 0](39), \pi[2 \to 0](30)) = (45, 39)$ . If p = (45, 39) then  $\mathbb{B}_{\gamma_0} = \{18, 21\}$ . which is disjoint with  $\mathbb{B}_{\pi_3} = \{39, 36, 27\}$ . We have  $\mathbb{B}_{\gamma_1} = \{18\}$ . So we have  $\mathbb{B}_{\eta_3} = \mathbb{B}_{\pi_3} \cup \mathbb{B}_{\gamma_0} = \{39, 36, 27, 21, 18\}$  and  $\mathbb{B}_{\eta_4} = \mathbb{B}_{\pi_4} \cup \mathbb{B}_{\gamma_1} = \{36, 33, 24, 18\}$ . For all other j, we have  $\mathbb{B}_{\eta_j} = \mathbb{B}_{\pi_j}$ .

- 4. Now  $\sigma = (51, 15) \circ (48, 12) \circ (54, 45) \circ (33, 24) \circ (39, 30)$ . All  $\mathbb{B}_{\pi_j}$ 's are the corresponding  $\mathbb{B}_{\eta_j}$ 's of the previous iteration. Let  $\sigma' = (18, 9)$ . Now  $(\pi[3 \rightarrow$

$0](18), \pi[3 \to 0](9)) = (18,9).$  If p = (18,9) then  $\mathbb{B}_{\gamma_0} = \{45,48,51\}$ . which is disjoint with  $\mathbb{B}_{\pi_4} = \{36,33,24,18\}$ . We have  $\mathbb{B}_{\gamma_1} = \{48\}$  and  $\mathbb{B}_{\gamma_2} = \{45\}$ . So we have  $\mathbb{B}_{\eta_4} = \mathbb{B}_{\pi_4} \cup \mathbb{B}_{\gamma_0} = \{51,48,45,36,33,24,18\}, \ \mathbb{B}_{\eta_5} = \mathbb{B}_{\pi_5} \cup \mathbb{B}_{\gamma_1} = \{48,33,30\}$  and  $\mathbb{B}_{\eta_6} = \mathbb{B}_{\pi_6} \cup \mathbb{B}_{\gamma_2} = \{45,30,27\}$ . For all other j, we have  $\mathbb{B}_{\eta_j} = \mathbb{B}_{\pi_j}$ . This completes the construction for all the  $s_i$ 's of the form 0 mod 3. Let us enumerate the sets explicitly

```

\begin{split} \mathbb{B}_{\eta_0} &= \{15, 18, 21, 24, 27, 30, 33, 36, 39, 42, 45, 48\} \\ \mathbb{B}_{\eta_1} &= \{12, 15, 18, 21, 24, 27, 30, 33, 36, 39, 42, 45\} \\ \mathbb{B}_{\eta_2} &= \{42, 39, 30, 27, 24, 9\} \\ \mathbb{B}_{\eta_3} &= \{39, 36, 27, 21, 18\} \\ \mathbb{B}_{\eta_4} &= \{51, 48, 45, 36, 33, 24, 18\} \\ \mathbb{B}_{\eta_5} &= \{48, 33, 30\} \\ \mathbb{B}_{\eta_6} &= \{45, 30, 27\} \\ \mathbb{B}_{\eta_i} &= \{48 - 3j, 45 - 3j\}, \ \forall \ 7 \le j \le 11 \end{split}

```

This therefore constructs all the  $s_i$ 's of the PRESENT permutation that are congruent to 0 mod 3 in  $12 \cdot 64 = 768$  cycles. We can use a similar approach to construct  $\overrightarrow{Sel}$  vectors for the  $s_i$ 's that are congruent to 1,2 mod 3, that can operate in  $8 \cdot 64 = 512$  cycles each. After padding of each of them to 768 cycles, a simple application of lemma 8 and corollary 3, allows us to construct the  $\overrightarrow{Sel}$  vector for the composition of all the  $s_i$ 's by computing  $\overrightarrow{Sel}_{0 \text{ mod } 3}$   $\overrightarrow{Sel}_{1 \text{ mod } 3}$   $\overrightarrow{Sel}_{2 \text{ mod } 3}$  that operates in just 768 cycles. Table 14 in the appendix lists the  $\mathbb B$  vectors for all the  $s_i$  transpositions that are 1,2 mod 3. Using a similar approach one can construct a similar  $\overrightarrow{Sel}$  vector for the composition of all  $t_i$ 's that operate in  $11 \cdot 64 = 704$  cycles. The  $\mathbb B$  vectors for the  $s_i$  transpositions are also listed in Table 14. Since our strategy is to execute the composition of the  $t_i$ 's followed by the  $s_i$ 's this approach takes 704 + 768 = 1472 cycles, which is the best we could manage.

## 4 The PRESENT circuit

Using the mathematical background presented in the previous section, we present our construction of the PRESENT circuit. Note that the sequence of operation in PRESENT are as follows:

## PRESENT Datapath PRESENT Keypath 1. For $i = 1 \rightarrow 31$ do 1. For $i = 1 \rightarrow 32$ do addRoundkey(STATE, $K_i$ ) $K_i = [k_{79}, k_{78}, \dots, k_{16}]$ sBoxLayer(STATE) $[k_{79}, k_{78}, \dots, k_1, k_0] \leftarrow [k_{18}, k_{17}, \dots, k_{20}, k_{19}]$ pLayer(STATE) $[k_{79}, k_{78}, k_{77}, k_{76}] \leftarrow S[k_{79}, k_{78}, k_{77}, k_{76}]$ 2. addRoundkey(STATE, $K_{32}$ ) $[k_{19}, k_{18}, k_{17}, k_{16}, k_{15}] \leftarrow [k_{19}, k_{18}, k_{17}, k_{16}, k_{15}] \leftrightarrow [k_{19}, k_{18}, k_{17}, k_{16}, k$

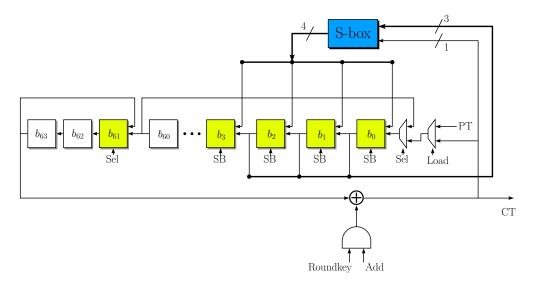

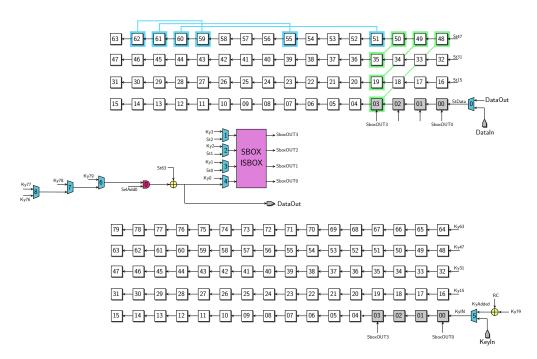

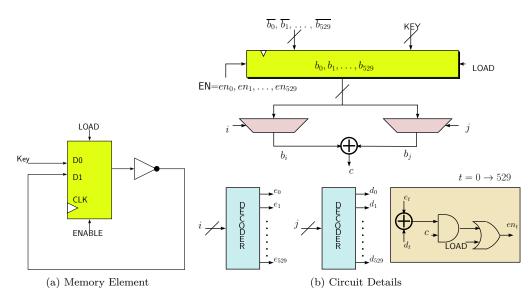

The circuit for the datapath and the keypath are described in Figures 4 and 5 respectively. Note that although it appears that the circuit employs two s-boxes, one for the data and keypaths each, in fact there is only one s-box circuit with a multiplexer in front which accepts inputs from the state and key registers at different periods in the encryption cycle. In order to explain the circuit operations, it is most instructive to give a cycle by cycle explanation of the flow of data in the registers.

Figure 4: The PRESENT datapath

**First 80 cycles:** In this period the plaintext and key are loaded onto the state and key registers bit by bit. We initiate a register **Cycle** which is reset to zero at the end of the key and plaintext loading.

Cycle 0 to 63: This period is used for adding the roundkey to the state bits and then a subsequent S-box operation. Although key addition and the subsequent register updates are done bitwise, it is possible to execute the 4-bit S-box operation by using the idea introduced in [JMPS17]. In Figure 4, we can see that the last 4 flip-flops in the circuit are in fact scan flip-flops which will help in the S-box operation. In the first 3 cycles of every 4-cycle period, the SB signal that controls these flip-flops are kept at zero so that in these 3 cycles the updated value is the addition of the corresponding state and keybits without the S-box operation. In the 4th cycle of this 4-cycle period, the SB signal is changed to 1 so that 4 bit output of the S-box is updated en-masse in this cycle.

**Cycle 64 to 1535:** The next 1472 cycles are used to implement the permutation layer as explained in the previous sub-section. The Sel port that controls the  $61^{st}$  flip-flop is fed the signals from the  $\overrightarrow{Sel}$  vector constructed in the previous section. The **Cycle** register is reset to zero at the end of this period.

The above procedure is repeated 31 times. In the  $32^{nd}$  iteration the first 64 cycles are used for the final roundkey addition operation and the ciphertext is available at the output of the xor gate that does the key addition. The keypath operations are slightly more involved. We need to perform the key update operations correctly, and at the same time ensure that the correct roundkey bit is available during the roundkey addition operation. The key update operation rotates the 80-bit key towards the left by 61 bits, then applies the s-box to a fixed nibble and then adds the round-constant to another fixed 5 bit chunk. The main concern therefore is to ensure that after the completion of a round, which in this case consists of 1536 cycles, the key is rotated by exactly 61 bits. It may have been possible to achieve this using a gated clock in the key registers that freezes the update operations for certain period of time. But clock gating requires some logic of its own and our intention was to see if we could achieve the required functionality without resorting to gating. Note that if we were to let the key register rotate uninterrupted for 1536 cycles, we would achieve a left key rotation of 1536 mod 80 = 16 bits. However if we rotate the register for  $\beta$  cycles such

Figure 5: The PRESENT Keypath

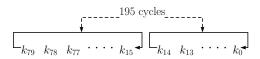

that  $\beta \equiv 61 \mod 80$  and somehow freeze the rotation for the remaining  $1536 - \beta$  cycles, we would achieve the required functionality. We chose  $\beta = 1341$ , which would require freezing the rotation operation for 195 cycles. To achieve this we use a scan flip-flop in the  $15^{th}$  location, controlled by a Rtx signal. When the Rtx signal is 1, the key register performs internal rotation between the first 65 and the next 15 bit chunks as shown in the following figure.

Since 195 is a multiple of both 15 and 65, such internal rotation when performed for 195 clock cycles, results in the identity function, and so we achieve our end objective of arresting rotation for exactly 195 cycles. For this purpose, one can choose any 195 of the 1536 cycles used in every round, except of course for the first 64 when the key addition is being performed. There are additional control signals KB that like SB in the case of of the state path controls the S-box operation in the key registers. And the AddC signal controls addition with round constants. These signals are set to 1 at appropriate cycles to ensure the respective functionalities.

## 4.1 Area and throughput results

The number of cycles taken to compute the encryption is therefore  $80+1536\cdot 31+64=47760$ . This is around 24 times slower than the implementation in [JMPS17]. Assuming that the Sel vector is stored as look-up-table within the circuit, then after synthesizing the circuit using the STM 90nm standard cell library, the synthesized circuit occupies logic area of around 943 GE which is also 100 GE more than the implementation in [JMPS17]. This is much more than we expected because of the following reason:

- A single round requires the Sel signal to be micro-controlled for 1472 cycles. This can only be done if the corresponding bit values are available as a lookup table inside the circuit.

- This requires around 200 B of storage and as seen in Figure 17, it requires around 170 GE of circuit area.

Thus, the 2 scan flip-flop circuit proves counterproductive and is of only theoretical interest.

## 4.2 Circuit for combined encryption and decryption

The approach outlined in the previous section is surprisingly effective when we try to implement a PRESENT circuit that can offer the combined functionalities of encryption and decryption. As already pointed out in [BBR16, BBR17a, JMPS17], such circuits are useful in implementing modes of operation like ELmD, CBC that require access to both the block cipher and its inverse operation. Our strategy to execute the PRESENT permutation P was to first execute the transpositions  $t_i$  in any order and then the transpositions  $s_i$  again in any order. In order to execute the inverse permutation  $P^{-1}$  it is enough to reverse the order: first execute the  $s_i$ 's followed by the  $t_i$ 's as explained below.

In order to understand why this is so, let us denote the composition of all  $s_i$ 's as  $\mathcal{S}$  and the composition of all  $t_i$ 's as  $\mathcal{T}$ , so that we have  $P = \mathcal{S} \circ \mathcal{T}$ . Both  $\mathcal{S}$  and  $\mathcal{T}$  are compositions of disjoint transpositions. Transpositions are involutary functions, which is to say they are self-inverses. Since all the  $t_i$ 's in  $\mathcal{T}$  are disjoint,  $\mathcal{T}^{-1}$  is again the composition of all the  $t_i$ 's therefore equal to  $\mathcal{T}$ . The same is true for  $\mathcal{S}$ . So we have  $P^{-1} = \mathcal{T}^{-1} \circ \mathcal{S}^{-1} = \mathcal{T} \circ \mathcal{S}$ . Thus the inverse permutation can be executed on the same circuit by shuffling around the  $\overline{\mathsf{Sel}}$  vector. There are however a few additions to the combined circuit that are listed below:

- There is an additional circuit for the PRESENT inverse S-box.

- The order of operations in the decryption process is listed as follows:

## PRESENT Datapath

## PRESENT **Keypath**

- 1. addRoundkey(STATE, $K_{32}$ )

- 2. Inv-pLayer(STATE)

- **3.** For  $i = 31 \to 2$  **do**

${\bf Inv\text{-}sBoxLayer(STATE)}$

$\mathtt{addRoundkey}(\mathtt{STATE}, K_i)$

Inv-pLayer(STATE)

- 4. Inv-sBoxLayer(STATE)

- **5.** addRoundkey(STATE, $K_1$ )

- 1.  $K_{32} = [k_{79}, k_{78}, \dots, k_{16}]$

- **2.** For  $i = 31 \to 1 \text{ do}$

$[k_{19}, k_{18}, k_{17}, k_{16}, k_{15}] \leftarrow [k_{19}, k_{18}, k_{17}, k_{16}, k_{15}] \oplus i$

$[k_{79}, k_{78}, k_{77}, k_{76}] \leftarrow S^{-1}[k_{79}, k_{78}, k_{77}, k_{76}]$

$[k_{79}, k_{78}, \dots, k_1, k_0] \leftarrow [k_{60}, k_{59}, \dots, k_{62}, k_{61}]$

The sequence of operations during decryption is slightly different. So let us look at the sequence of operations in each cycle:

First 80 cycles: As usual the ciphertext and key are loaded onto the respective registers.

Cycle 0 to 63: In the round immediately after ciphertext loading, we perform only bitwise round key addition in this period. However in all the subsequent rounds, we need to do an Inverse s-box operation before roundkey addition. This would require some incremental additions to the circuit. First of all we need a 4-bit xor to do the key addition instead of just a single bit xor in the encryption path. A four bit multiplexer is additionally required to select between the 4-bit updates during encryption and decryption. The logic circuit is explained diagrammatically in Figure 6.

**Cycle 64 to 1535:** The next 1472 cycles are used to implement the inverse permutation layer, with the S executed ahead of T.

Figure 6: Modified logic around the last 4 flip-flops to accommodate decryption

• The keyschedule involves addition by round constant followed by application of inverse s-box on a fixed nibble followed by rotation by 19 bits to the left. As before we need to try to rotate the key register for  $\beta \equiv 19 \mod 80$  cycles and somehow arrest the rotation for the remaining  $1536 - \beta$  cycles. We choose  $\beta = 1399$ , which requires stopping the rotation for 237 cycles. Again, we try to achieve this by breaking up the key into chunks of 79 and 1 bits and doing internal rotation within the key-chunks for 237 cycles. Since 237 is a multiple of 79 and 1, internal rotation for 237 cycles again gives the identity transformation which satisfies our end objective. In terms of hardware, this requires two extra multiplexers to do the internal rotation as shown in Figure 6.

The area occupied by the circuit when synthesized with the standard cell library of the STM 90nm CMOS process, is around 1040 GE. This is around 200 GE less than the previous best reported implementation of the combined circuit for PRESENT in [BBR17b], which occupies around 1240 GE. However the area is still high due to the inclusion of the control bits as a lookup table.

## 5 Application to GIFT

GIFT was a block cipher designed by Banik et al. [BPP $^+$ 17] and presented at CHES 2017, with a view to strengthen the cryptographic properties of PRESENT by redesigning the permutation layer and keyschedule. It is a block cipher with an SPN round function in which the linear layer is a bit permutation similar to PRESENT. The permutation function G is listed in table 9.

The following can be said about the function G:

- 1. It is a special permutation of type  $\kappa = 4$ .

- 2. It can be decomposed into fourteen 4-cycles and two 2-cycles all of which are pairwise disjoint. Additionally it has 4 fixed points.

- 3. Each 4-cycle can be decomposed into three transpositions  $s_i \circ t_i \circ u_i$ . The decomposition is shown in the following table.

| $\overline{i}$ | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| G(i)           | 0  | 17 | 34 | 51 | 48 | 1  | 18 | 35 | 32 | 49 | 2  | 19 | 16 | 33 | 50 | 3  |

| i              | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| G(i)           | 4  | 21 | 38 | 55 | 52 | 5  | 22 | 39 | 36 | 53 | 6  | 23 | 20 | 37 | 54 | 7  |

| i              | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| G(i)           | 8  | 25 | 42 | 59 | 56 | 9  | 26 | 43 | 40 | 57 | 10 | 27 | 24 | 41 | 58 | 11 |

| i              | 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| G(i)           | 12 | 29 | 46 | 63 | 60 | 13 | 30 | 47 | 44 | 61 | 14 | 31 | 28 | 45 | 62 | 15 |

Table 5: Specifications of GIFT bit-permutation layer.

| i | $c_i$           | $s_i \circ t_i \circ u_i$               | i  | $c_i$            | $s_i \circ t_i \circ u_i$             |

|---|-----------------|-----------------------------------------|----|------------------|---------------------------------------|

| 0 | (1, 17, 21, 5)  | $(5,17) \circ (17,21) \circ (1,5)$      | 8  | (11, 19, 55, 47) | $(19,47) \circ (19,55) \circ (11,47)$ |

| 1 | (2, 34, 32, 10) | $(10,34) \circ (34,42) \circ (2,10)$    | 9  | (13, 33, 25, 53) | $(13,25) \circ (25,53) \circ (13,33)$ |

| 2 | (3, 51, 63, 15) | $(15,51) \circ (51,63) \circ (3,15)$    | 10 | (14, 50, 46, 58) | $(14,46) \circ (46,58) \circ (14,50)$ |

| 3 | (4, 48, 12, 16) | $(12,16) \circ (16,48) \circ (4,16)$    | 11 | (20, 52, 60, 28) | $(28,52) \circ (52,60) \circ (20,28)$ |

| 4 | (6, 18, 38, 26) | $(18, 26) \circ (18, 38) \circ (6, 26)$ | 12 | (23, 39, 43, 27) | $(27,39) \circ (39,43) \circ (23,27)$ |

| 5 | (7, 35, 59, 31) | $(31,35) \circ (35,59) \circ (7,31)$    | 13 | (24, 36, 56, 44) | $(36,44) \circ (36,56) \circ (24,44)$ |

| 6 | (8, 32)         | (8,32) 0 0                              | 14 | (30, 54)         | (30, 54) ∘ ∘                          |

| 7 | (9, 49, 29, 37) | $(29,37) \circ (37,49) \circ (9,37)$    | 15 | (41, 57, 61, 45) | $(45,57) \circ (57,61) \circ (41,45)$ |

Table 6: Decomposition of the  $c_i$ 's in the GIFT permutation

As per the strategies outlined in the case of PRESENT, we try to implement all the  $u_i$ 's first, followed by the  $t_i$ 's and  $s_i$ 's, since as per lemma 3, we would have then constructed G. Furthermore for each of the  $u_i$ 's,  $t_i$ 's and  $s_i$ ' we construct composite  $\overline{\mathsf{Sel}}$  vectors by finding  $\overline{\mathsf{Sel}}$  vectors for each equivalence class modulo 4 and then doing a bitwise OR. Each of the transposition sets can be implemented in  $9 \times 64 = 576$  cycles. This implies that G can be executed in  $3 \times 576 = 1728$  cycles. The results are tabulated in Table 15 in the appendix.

## 5.1 Circuit details

Since the structure of GIFT is similar to PRESENT, the circuit for the datapath is exactly the same as in Figure 4, with the obvious exception that the scan flip-flop is used in the  $60^{th}$  instead of the  $61^{st}$  location. The sequence of operations in GIFT is only slightly different from PRESENT:

GIFT Datapath GIFT Keypath

1. For

$$i=1 \rightarrow 28$$

do

sBoxLayer(STATE)

pLayer(STATE)

pLayer(STATE)

$$K_i = [k_{127}, k_{78}, \dots, k_0]$$

For  $j=0 \rightarrow 7$ :  $L_j \leftarrow [k_{16j+15}, k_{16j+15}, \dots, k_{16j}]$

addRoundkey(STATE, $RK_i$ )

$$RK_i = L_1||L_0$$

$$L_7||L_6||\cdots||L_0 \leftarrow L_1 \gg 2||L_0 \gg 12||L_7||\cdots||L_2$$

So the sequence of operations in the datapath is as follows:

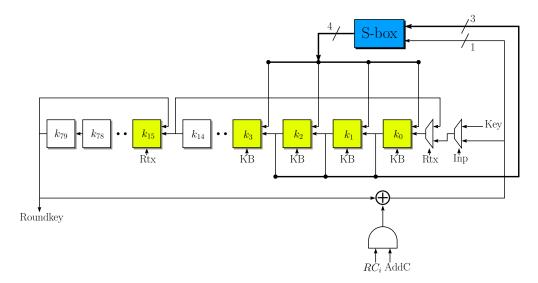

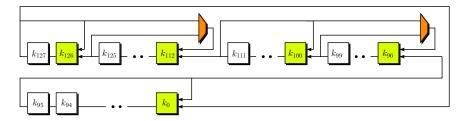

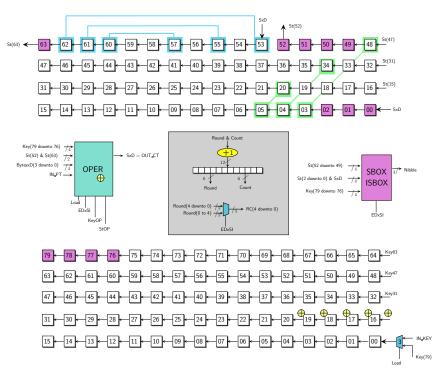

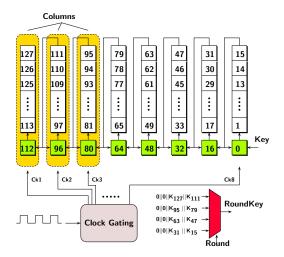

Figure 7: The GIFT key register

**First 128 cycles:** In this period the key is loaded onto the state and key registers bit by bit. In cycles 64 to 127, the plaintext is loaded onto the state register after performing the s-box operation. Thereafter we have 28 iterations of the following operations.

Cycle 0 to 1727: Used to compute the permutation layer.

**Cycle 1728 to 1791:** The next 64 cycles are used to compute add roundkeys and then perform the s-box operation of the next round.

Thus the total number of cycles taken for the encryption routine is  $128+28\times1792=50304$ . The keyschedule is slightly more complicated: it breaks up the current key into eight 16 bit words  $L_7$  to  $L_0$ .  $L_1$  and  $L_0$  are internally right rotated by 2, 12 bits respectively and the whole key is then right rotated by 32 bits. In other words this means internal left rotation of  $L_1$  and  $L_0$  by 14, 4 bits and overall left rotation by 96 bits. So we do the following:

- Let the key register rotate left for 96 cycles. After this  $L_1$  and  $L_0$  occupy the most significant 32 bits of the register  $(k_{127}$  to  $k_{96})$ .

- At this point of time we will partition the key register into chunks of 16  $(k_{127}$  to  $k_{112})$ , 16  $(k_{111}$  to  $k_{96})$  and 96 bits  $(k_{95}$  to  $k_0)$  and do an internal rotation for 288 cycles. Since  $1792 288 = 1504 \equiv 96 \mod 128$  this achieves our first objective of 96 bit left rotation.

- To achieve left rotation of  $L_1$  by 14 bits, we partition the 1st 16 MSBs into chunks of 2 ( $k_{127}$  to  $k_{126}$ ) and 14 ( $k_{125}$  to  $k_{112}$ ) bits and do an internal rotation in these 2 groups for 98 cycles, and do a normal rotation over ( $k_{127}$  to  $k_{112}$ ) over the remaining 288-98=190 cycles (see figure 7). Since 2 and 14 both divide 98, the rotation results in identity transformation. So the effective rotation is for 190  $\equiv$  14 mod 16 cycles.

- Similarly rotating  $L_0$  by 4 bits, we partition 2nd 16 MSBs into chunks of 12  $(k_{111}$  to  $k_{100})$  and 4  $(k_{99}$  to  $k_{96})$  bits. Internal rotation is carried out for in these smaller chunks 12 cycles. So effectively we rotate the 2nd chunk by 276  $\equiv$  4 mod 16 bits.

However the key addition in GIFT is quite complicated: neighboring key bits do not xor with neighboring state bits as in PRESENT. In fact, the designers recommend that  $\forall i \in [0,31]$  the  $i^{th}$  bit of  $L_1$  be xored with the  $(4i+2)^{nd}$  state bit and the the  $i^{th}$  bit of  $L_0$  be xored with the  $(4i+1)^{st}$  state bit. Thus, the circuit also requires a filter to extract the correct roundkey bit in every cycle, which increases the total area slightly. The circuit occupies 1132 GE which is around 200 GE higher than the implementation reported in [BPP+17], on account of the large control bit table required in the circuit.

## 5.2 Combined Circuit for encryption and decryption

The GIFT decryption circuit suffers from the same issues as the corresponding PRESENT circuit, and therefore the circuit for the combined decryption is same as the one outlined in

Figure 6. The only differences are in the order in which the functions are carried out. The following is the sequence of operations:

# GIFT Datapath GIFT Keypath 1. addRoundkey(STATE, $RK_{28}$ ) 2. inv-pLayer(STATE) 3. For $i=1 \rightarrow 28$ do $K_i = [k_{127}, k_{78}, \dots, k_0]$ For $j=0 \rightarrow 7$ : $L_j \leftarrow [k_{16j+15}, k_{16j+15}, \dots, k_{16j}]$ inv-sBoxLayer(STATE) $RK_i = L_1||L_0$ addRoundkey(STATE, $RK_i$ ) inv-pLayer(STATE) $L_7||L_6||\cdots||L_0 \leftarrow L_5||\cdots||L_0||L_7 \ll 2||L_6 \ll 12$

4. inv-sBoxLayer(STATE)

As expected the inverse permutation

As expected, the inverse permutation layer is constructed by executing the  $s_i$  transpositions first, followed by the  $t_i$ 's and then the  $u_i$ 's. The cycle by cycle execution of operations is as follows:

First 128 cycles: In this period the key is loaded onto the state and key registers bit by bit. In cycles 64 to 127, the plaintext is loaded onto the state register without performing the inverse s-box operation. Thereafter the following operations are executed 28 times.

**Cycle 0 to 63:** Used for executing the inverse s-box operations followed by roundkey addition as shown in Figure 6. As in PRESENT only in the first round, the inverse s-box operation is omitted.

Cycle 64 to 1791: Used for executing the inverse p-layer.

After this, the GIFT decryption process requires one more inverse s-box operation. Hence the decryption operation requires an additional 64 cycles to complete. The key schedule for decryption can be carried out using the same circuit as in Figure 7. We need left rotation of  $L_7$ ,  $L_6$  by 2, 12 bits followed by a left rotation by 32 bits. At the beginning of the round cycle when  $L_7$ ,  $L_6$  still occupy the 32 MSBs in the key register we do internal rotation for 96 cycles. It is easy to see to verify that this will achieve left rotation by 32 bits. In these 96 cycles, we do further internal rotation between the 2 and 14 bit chunks  $(k_{127}$  to  $k_{126}$  and  $k_{125}$  to  $k_{112}$ ) for 14 cycles, and for 36 cycles between the 12 and 4 bits chunks  $(k_{111}$  to  $k_{100}$  and  $k_{99}$  to  $k_{96}$ ) for 36 cycles. This is sufficient to achieve the required functionalities in the inverse keyschedule. The circuit occupies 1290 GE in hardware and is the first reported synthesis results for the combined circuit for this block cipher.

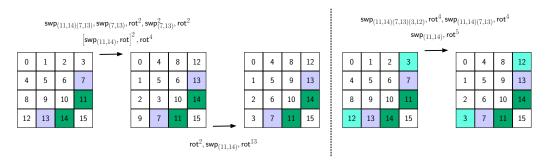

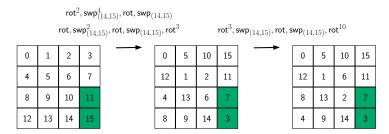

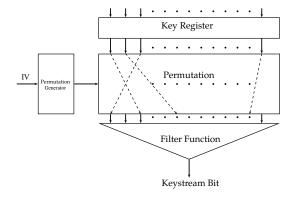

## 6 Adding more scan flip-flops