# The Area-Latency Symbiosis: Towards Improved Serial Encryption Circuits

Fatih Balli, Andrea Caforio and Subhadeep Banik

LASEC, École Polytechnique Fédérale de Lausanne, Switzerland {fatih.balli,andrea.caforio,subhadeep.banik}@epfl.ch

**Abstract.** The *bit-sliding* paper of Jean et al. (CHES 2017) showed that the smallest-size circuit for SPN based block ciphers such as AES, SKINNY and PRESENT can be achieved via bit-serial implementations. Their technique decreases the bit size of the datapath and naturally leads to a significant loss in latency (as well as the maximum throughput). Their designs complete a single round of the encryption in 168 (resp. 68) clock cycles for 128 (resp. 64) bit blocks. A follow-up work by Banik et al. (FSE 2020) introduced the *swap-and-rotate* technique that both eliminates this loss in latency and achieves even smaller footprints.

In this paper, we extend these results on bit-serial implementations all the way to four authenticated encryption schemes from NIST LWC. Our first focus is to decrease latency and improve throughput with the use of the swap-and-rotate technique. Our block cipher implementations have the most efficient round operations in the sense that a round function of an n-bit block cipher is computed in exactly n clock cycles. This leads to implementations that are similar in size to the state of the art, but have much lower latency (savings up to 20 percent). We then extend our technique to 4-and 8-bit implementations.

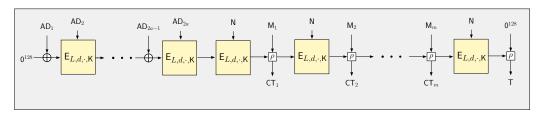

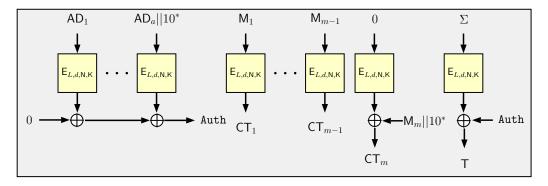

Although these results are promising, block ciphers themselves are not end-user primitives, as they need to be used in conjunction with a mode of operation. Hence, in the second part of the paper, we use our serial block ciphers to bootstrap four active NIST authenticated encryption candidates: SUNDAE-GIFT, Romulus, SAEAES and SKINNY-AEAD. In the wake of this effort, we provide the smallest block-cipher-based authenticated encryption circuits known in the literature so far.

**Keywords:** Lightweight, Latency, Swap, Rotate, Block Cipher, Authenticated Encryption, NIST LWC, AES, SKINNY, GIFT, SUNDAE, SAEAES, SKINNY-AEAD, Romulus, Grain-128AEAD

#### 1 Introduction

The number of applications that rely on standard cryptographic primitives to establish a secure communication channel grow larger each day. Given the large variety of platforms these applications are run by, the available device resources spread to a large spectrum. In this spectrum, those applications related to IoT, sensor networks, RFID, vehicle-to-vehicle communication suffer from having tight security budgets. They hence rely on the future promise by an emerging field, that is *lightweight cryptography*, where new standards of primitives that are cheaper in terms of hardware footprint, energy, power and latency are anticipated. NIST's ongoing standardization process for lightweight cryptography (NIST LWC) clearly reflects the vivid effort in this domain. The candidates, 32 of which are elected for the second round, provide new designs for an authenticated encryption primitive, with the final goal of attaining security and lightweightness at the same time.

| Candidate   | P          | rimary           | A           | lternative           |              |

|-------------|------------|------------------|-------------|----------------------|--------------|

|             | cipher     | size (block+key) | cipher      | size (block $+$ key) | cipher calls |

| COMET       | AES        | 128+128          | CHAM, Speck | 64/128+128           | enc          |

| ESTATE      | TweAES     | 128 + 128        | TweGIFT     | 128 + 128            | enc+dec      |

| ForkAE      | ForkSKINNY | 128 + 288        | ForkSKINNY  | 64/128+192/256/288   | enc+dec      |

| GIFT-COFB   | GIFT*      | 128 + 128        | -           | =                    | enc          |

| HYENA       | GIFT       | 128 + 128        | -           | -                    | enc          |

| LOTUS-AEAD  | TweGIFT    | 64 + 128         | -           | -                    | enc          |

| mixFeed     | AES        | 128 + 128        | -           | -                    | enc          |

| Pyjamask    | Pyjamask   | 128 + 128        | Pyjamask    | 96 + 128             | enc          |

| Romulus     | SKINNY     | 128 + 384        | SKINNY      | 128 + 256/384        | enc          |

| SAEAES      | AES        | 128 + 128        | -           | =                    | enc          |

| Saturnin    | Saturnin   | 256 + 256        | -           | -                    | enc          |

| SKINNY-AEAD | SKINNY     | 128 + 384        | SKINNY      | 128 + 256/384        | enc          |

| SUNDAE-GIFT | GIFT*      | 128+128          | -           | - '                  | enc          |

Table 1: The list of second-round NIST LWC candidates that are based on block ciphers. GIFT refers to the original block cipher from [BPP<sup>+</sup>17], and GIFT\* refers to the version that assumes different ordering of the input bits and the key [BCI<sup>+</sup>19, BBP<sup>+</sup>19].

LIGHTWEIGHT METRIC. In the crypto community, the definition of security is defined with rigor, generally by resorting to algorithmic games. However, the term *lightweight* does not hold up to the same precision.

First, there is a question of which metric should be prioritized. In practice, each application is most concerned about the particular implementation aspect of the cryptographic primitive that conflicts with its own tight-budget. For battery-powered sensors, the energy spent per encrypted bit is a matter of priority, and directly determines how long the battery lasts. Sometimes, multiple metrics must be taken into consideration. As an example, an RFID device might prioritize power, but at the same time its silicon area footprint is also crucial.

Secondly, there is a question of how to quantify this metric. This is highly dependent on how the scheme is implemented, e.g. as an application-specific integrated circuit (ASIC), on a field-programmable gate array (FPGA) or programmed to a microprocessor. This further depends on the specific details. For instance, the transistor size of the cell library in ASIC plays a key role in area, power consumption as well as the response time of the gates.

In this paper, the term lightweight refers to the combination of both the area (in terms of gate-equivalence GE) and the latency (in terms of clock cycles) of an architecture realized as an ASIC. We believe that these two metrics are most easily reproducible, in the sense that given two implementations A and B, there is a methodological and fair approach to decide which one performs better<sup>1</sup>. In our implementations, we prioritize both area and latency. Therefore, our goal is to remain in the same area budget (or have further reductions if possible) of the ultra-small (i.e. 1/4/8-bit-datapath) implementations and reduce the latency (i.e. the number of clock cycles) as much as possible.

Reducing latency is an important goal, as it directly translates into a throughput gain, as well as a reduction in the energy consumption<sup>2</sup>. Given the variety of application profiles, it is worth noting that the ideal goal from an implementation standpoint is to lower the cost in one or few metrics so that the design is sufficient to meet the expectation of most (if not all) applications.

$<sup>^1\</sup>mathrm{GE}$  measurements are not perfectly reliable across different technology libraries. For fairness, we compare GE-sizes of two implementations A and B synthesized in the same technology library.

<sup>&</sup>lt;sup>2</sup>The energy consumption is lower, if we assume that the power consumption remains same. This holds true for most of our implementations.

Mode of operations. Among the active second round candidates, 13 out of 32 are based on block ciphers. These candidates simply design a mode of operation around a given block cipher to function as an authenticated encryption scheme. From Table 1, note that:

- 4 candidates use either the standard or a tweaked version of AES as the primary choice. These are COMET, ESTATE, mixFeed, SAEAES [GJN19, CDJ<sup>+</sup>19a, CN19, NMMaS<sup>+</sup>19].

- 3 candidates use either the standard or a forked version of SKINNY as the primary choice. These are ForkAE, Romulus, SKINNY-AEAD [ALP+19, IKMP19, BJK+19].

- 2 candidates use either the standard or a tweaked version of 128-bit variant of GIFT. Namely, ESTATE uses the tweaked version of GIFT as an alternative choice [CDJ<sup>+</sup>19a], whereas HYENA uses the original version [CDJN19, BPP<sup>+</sup>17]. Besides these two, LOTUS-AEAD also employs a tweaked 64-bit variant of GIFT [CDJ<sup>+</sup>19b, BPP<sup>+</sup>17].

- 2 candidates use GIFT\*. These two candidates are GIFT-COFB and SUNDAE-GIFT [BCI+19, BBP+19]. The difference between GIFT\* and GIFT is that the former assumes a different indexing of the input and output bits. We denote their modified version with GIFT\*, as it leads to a significant difference from a design and implementation perspective (but remains equivalent in terms of cryptanalysis).

- Pyjamask and Saturnin are the exceptions to the popular approach, as they bring their own dedicated block cipher designs into the standardization [GJK<sup>+</sup>19, CDL<sup>+</sup>19].

Given the modular approach taken by these candidates, one can pose the two following questions, which relates directly to their lightweight performance: (1) How lightweight is the block cipher employed at the core? (2) What is the cost of the surrounding mode of operation? Our work and results respond to these two significant questions.

BOTTLENECK OF STORAGE. Most low-area implementations of SPN-based block ciphers eventually face a bottleneck of storage, quite similar to the fashion in which they are observed in hash functions [BLP<sup>+</sup>08]. Namely, all implementations (except those that are fully unrolled) need to store the key and the cipher state during the encryption operation. For a block cipher with  $\ell_b$ -bit block and  $\ell_k$ -bit key, this typically requires the use of  $\ell_b + \ell_k$  flip-flops. More concretely, the area-cost of storing 256-bit corresponds to 1088 GE, 832 GE and 1451 GE for the cell libraries UMC 90 nm, STM 90 nm and NanGate 45 nm respectively. It naturally follows that for the smallest implementations of AES (resp. SKINNY-128-128, GIFT), the 73% (resp. 83%, 69%) of the circuit is due to merely D flip-flops [JMPS17, BPP<sup>+</sup>17]. Therefore, the state-of-the-art ultra-small ASIC implementations of block ciphers contain mostly storage elements, and space for further area optimizations is limited. We take this as an indicator that we should divert our focus to the other aspects of the circuit while remaining in the same area budget.

#### 1.1 Area, Latency and Energy

Serialized implementations generally have poor energy efficiency as explained in [BBR15]. There are two principal reasons for this:

• These circuits generally require larger latency than round-based circuits. For example, Atomic-AES [BBR16], which closely follows the design by Moradi et al. [MPL+11], has a datapath of 8 bits, occupies around 2060 GE, and requires 226 clock cycles to execute one block of AES encryption. The latency is twentyfold compared to 11 clock cycles it takes for the round-based circuit to do the same, but it occupies around 4 times less area than the round-based circuit, as the latter costs 8000 GE. Due to this, the byte-serial circuit takes around 7-8 times more energy than a round-based

circuit (allowing for some variations due to circuit design and the choice of the CMOS library).

Any serialized circuit is required to perform many more register write operations.

A round-based circuit overwrites its internal register 11 times, once per clock cycle, with intermediate round output. Consider on the other hand any byte-serial circuit (or more specifically the Atomic-AES circuit). A simple operation

$$b_0, b_1, \ldots, b_{15} \longrightarrow b_1, \ldots, b_{15}, S(b_0 \oplus k_0)$$

which basically rotates the state by one byte, and substitutes the least significant byte with the output of the AddRoundkey and S-box on the byte  $b_0$ , requires an entire register overwrite. As is obvious, this needs to be done at least 15 more times for each byte  $b_i$  and then again 4 times for the MixColumns operation for each of the 10 rounds. Since each register write requires finite energy, it is obvious that the energy budget shoots up in the process. The energy consumption proportionally increases the more we try to reduce the length of the datapath. Therefore, a bit-serial datapath would by a similar logic, be even more expensive energy-wise.

However, this logic does not extend to power consumption, as power is the time derivative of energy and essentially the rate of energy spent per unit of time. The fewer number of gates a circuit consists of, it is more often the case that its power footprint becomes smaller. As a consequence, serialized circuits should not be used in situations where energy efficiency is a prime concern, but can still be favored in scenarios where power is the target metric. For example, for battery-driven devices energy consumption is a top priority, whereas for applications like medical implants and passive RFID tags (that typically do not use the latest CMOS technology), power consumption is very important. In implantable devices, power is a more crucial metric, as the wearer certainly can not tolerate any rise in operating temperature as a side effect of high power consumption over a number of cycles. Although energy is an important metric, our research direction is directed towards these applications that cannot ignore area and power constraints.

There is ample scope for optimization, in an engineering sense, that allows us to strive to design better circuits, no matter how narrow the scope to do so might initially seem. Again, let us go to the example of Atomic-AES, which is a byte-serial circuit that spends 21 cycles to execute one AES round computation. It is well known that Atomic-AES uses only one S-box circuit. It is not feasible to design an AES circuit with a single S-box that completes a round in less than 20 clock cycles. This is obvious, since one AES round requires 20 S-box accesses per round (16 in the substitution layer and 4 in the key update). In this respect, the Atomic-AES circuit is close to optimum in terms of latency. Now, one way to convert a byte-serial circuit to bit-serial could be to chain the flip-flops in each byte register sequentially, so that it takes 8 clock cycles instead of 1 to transfer one byte of information. This way, the conversion of the Atomic-AES circuit into bit-serial would require  $21 \times 8 = 168$  cycles to execute one AES round. Is it possible to actually achieve this circuit (or do better)? This question was already answered affirmatively by Moradi et al. [JMPS17], which constructed a circuit that performed one AES round in 168 clock cycles. What is the lowest possible number of cycles in which we can hope to do one AES round in a bit-serial circuit? A little thinking will tell us that we can not possibly do it in fewer than 128 cycles, which is the block size of AES, since each bit in the state needs to be rotated around the state pipeline at least once, and this requires 128 clock cycles. One of the things we investigate in this paper is whether it is possible to attain this minimum.

#### 1.2 Motivation

In comparison to their 8-bit (or even 32/128-bit) counterparts, bit-serial implementations offer lower throughput, as they execute only single bit of operation in each clock cycle

[JMPS17, BBR17, BBRV20]. Then, one might wonder whether this latency loss is justified for the sake of reducing area, and whether these designs will see industrial applications. Let us elaborate on that point briefly, and explain our motivation to further pursue 1-bit-serial implementation techniques.

Even though the silicon fabrication process makes progress each year, some of the applications lag behind in catching up with the newer smaller-size transistor technologies, mostly because of the costs involved in establishing the fabrication process. While the smallest-size transistors see a rather short time to catch up with the market for personal computers and smartphones, this is not true for many low-cost devices, which prioritize the price. These devices mainly include those that are bought in bulk quantities such as electronic identity or public transportation cards, electronic event tickets etc. More concretely, take MIFARE brand of products by NXP Semiconductors as an example. Among this series, MIFARE Ultralight is sold as the most cost-effective product, because the cost of system ownership as well as the individual card prices are the lowest. These devices are protected with 32-bit passwords against malicious writes, and use 3DES + CBC to achieve authentication through a shared secret key [MIFb, MIFa]. Enabling up-to-date lightweight symmetric cryptography, in particular an authenticated encryption scheme with low-area footprint on these platforms is of great importance, because they are used by thousands, if not millions, of people. The correct application and engineering of cryptography on these devices would fix some of the previous design flaws [GdKGM<sup>+</sup>08, dKGHG08].

Also note that one of the benefits of bit/byte-serial circuits with respect to area reduction is that the circuit requires fewer number of scan flip-flops (which is typically larger than a flip-flop without scan functionality) to construct. However, consider design for testability (DFT) features like scan chains which, when incorporated in a circuit, would require all flip-flops to have the scan functionality in order to accommodate the scan-chain path. In spite of this, serialized circuits have remained popular in the literature and has been employed in numerous papers. Why is this so? Note that for most libraries the compiler implements a scan flip-flop as a multiplexer (MUX) with a simple flip-flop (without reset). So in this context, reducing the number of scan flip-flops is really equal to reducing the extra MUXes needed in the circuit. If a scan-chain DFT functionality is still incorporated on top of it, then every flip-flop used in the circuit will require an additional input port (along with a MUX), irrespective of whether it was designed as a scan flip-flop or normal flip-flop, to accommodate the scan chain used for testing. Therefore including DFT will always increase the area of the circuit by around n 2-input MUXes (where n is the number of storage bits in the circuit), irrespective of the number scan flip-flops in the circuit without DFT. This is the reason why reduction of the number of scan flip-flops is done in many papers in the community and it remains popular.

It should also be noted that, for most of the aforementioned applications, bit-serial implementations can provide sufficient throughput. For instance, our bit-serial authenticated encryption implementations have maximum throughput of roughly 4-10 Mbit/s in a rather old STM 90 nm library, which reaches up to 90-145 Mbit/s in a newer NanGate 15 nm library. This throughput already exceeds the communication bandwidth of these low-cost devices. And lastly, the goal of our effort is to discover new techniques that can also be applied to 4/8-bit implementations. In that regard, we also provide 4/8-bit implementations that are small but better in terms of latency compared to previous work.

COMPARISON WITH RELATED WORK: Two previous papers that immediately evokes comparison with our work are [JMPS17, BBRV20]. The former was the first paper to propose a 1-bit datapath implementation of AES, PRESENT and SKINNY family. However none of the implementations reported in this paper achieved a latency per round figure equal to the block size of the underlying block cipher. One of the reasons for this is that they approach the entire round function as a monolithic entity, i.e. all the algebraic operations in the round were completed in the time period allotted for the round. Large

amount of the engineering in this paper is devoted towards investigating what happens if we flirt with these boundaries by executing some operations of round i in the time period allotted to round i+1 while maintaining correct functionality. As it turns out, when we do this efficiently, we can limit latency per round (in clock cycles) to the block size and that is exactly the mathematical challenge we faced in this work. To make things clearer, note that [JMPS17] reports a bit-serial implementation of AES which completes a round in 168 cycles. 128 clock cycles are used to rotate bits across the state pipeline and perform AddRoundKey and SubBytes operations simultaneously. Precisely 8 cycles are used for ShiftRows and 32 more for MixColumns. However, we observed that we could be more flexible in the scheduling of operations, which is to say neither do we have to wait for the AddRoundKey and SubBytes operation to be completed on the entire 128-bit state to begin ShiftRows, nor wait for the ShiftRows to complete to begin MixColumns. When a group of bits in the state have undergone AddRoundKey and SubBytes, we can already begin ShiftRows on those bits immediately and the same holds for the scheduling of MixColumns vis-à-vis ShiftRows. In the process of developing this technique, we find that not all operations of a round is finished in the time allocated for the round, and so we improvise and try to get them done in the next round, while trying to maintain functionality at all times.

A preliminary version of the aforementioned technique was applied by Banik et al. specifically to the permutation layers of GIFT-64 and PRESENT, but without generalization to other family of block ciphers [BBRV20]. The previous work does not make it clear how to generalize the technique to implementations of higher-bit datapaths, nor how to extend it to other family of block ciphers. However as we will describe in Section 3, our approach takes the idea further from bit-serial to arbitrary-size datapath in a seamless fashion. In other words, from the bit-serial implementation the circuit designer is able to infer how to both physically assemble and schedule operations of the circuit of higher-size datapath.

CONTRIBUTIONS. In the first part of the paper, we provide 1/4/8-bit-serial architectures for the popular 128-bit block size variants of the block ciphers AES, SKINNY, GIFT\* and GIFT, which are popular among NIST candidates. Our implementations can be employed by 10 candidates out of 13 listed in Table 1. Our approach has the following benefits, and the detailed comparison with the state of the art is summarized in Table 2:

- In terms of circuit area, each of our block cipher implementations is an evident contender to be the smallest implementation.

- Each implementation fully utilizes both the state and the key pipelines. With 1-bit datapath, each round consisting of 128-bit is executed exactly in 128 clock cycles. This ensures that we get the maximum throughput from 1-bit-serial implementation. This leads to an approximately 20% reduction in latency (in clock cycle units) over the circuits reported by the previous work [JMPS17, BPP+17] (note that the AES, SKINNY, GIFT circuits in these papers report a latency of 168, 168, 160 cycles per round respectively). Our circuit design is novel in the sense that both pipelines are continuously active.

- With 8-bit datapath, each round consisting of 128 bits is executed exactly in 16 clock cycles. This leads to a roughly 20% reduction in latency over the circuits reported in [JMPS17, BBR16] (note that the AES, SKINNY, GIFT circuits in these papers report a latency of 21, 21, 20 cycles per round respectively).

- Each implementation respects the standard ordering of input and output bits. We do not make a non-standard assumption on the ordering of the bits to reduce the area and latency. Namely, we ensure that an implementation from our paper is readily usable from a NIST LWC candidates without having to modify and deal with the ordering the bits. Some implementations of AES, e.g. [MPL+11, JMPS17, BBR16, BBR17],

|                                 | Area (     | GE)    | Power      | $(\mu W)$            | Latency | (cycles) | Energy (n. | J/128-bit)           |                   |

|---------------------------------|------------|--------|------------|----------------------|---------|----------|------------|----------------------|-------------------|

| Block cipher                    | NanGate 45 | UMC 90 | NanGate 45 | UMC 90               | round   | total    | NanGate 45 | UMC 90               | Ref.              |

|                                 |            |        | @ 100 KHz  | $@~100~\mathrm{KHz}$ |         |          | @ 100 KHz  | $@~100~\mathrm{KHz}$ |                   |

| AES (standard)                  | 1974       | 1600   | 102.4      | 0.55                 | 128     | 1408     | 1441.8     | 7.7                  | this work, Sec. 4 |

| AES (non-standard)              | 1982       | 1596   | 100.2      | 0.67                 | 168     | 1776     | 1779.6     | 11.9                 | [JMPS17]          |

| AES (standardized) <sup>a</sup> | 2029       | 1641   | -          | -                    | 168     | 1904     |            |                      | [JMPS17]          |

| SKINNY-128-128                  | 1748       | 1355   | 87.7       | 0.43                 | 128     | 5248     | 4602.0     | 22.6                 | this work, Sec. 5 |

| SKINNY-128-128                  | 1740       | 1363   | 86.7       | 0.56                 | 168     | 6976     | 6045.4     | 39.1                 | [JMPS17]          |

| SKINNY-128-256                  | 2502       | 1927   | 125.0      | 0.62                 | 128     | 6272     | 7837.5     | 38.9                 | this work, Sec. 5 |

| SKINNY-128-256                  | 2501       | 1937   | 123.5      | 1.15                 | 168     | 8448     | 10432.4    | 97.2                 | [JMPS17]          |

| SKINNY-128-384                  | 3263       | 2518   | 162.8      | 0.82                 | 128     | 7296     | 11877.2    | 59.8                 | this work, Sec. 5 |

| SKINNY-128-384                  | 3260       | 2508   | 160.0      | 1.55                 | 168     | 9920     | 15875.0    | 153.8                | [JMPS17]          |

|                                 | STM 90     | UMC 90 | STM 90     | UMC 90               |         |          | STM 90     | UMC 90               |                   |

|                                 |            |        | @ 10 MHz   | @ 10 MHz             |         |          | @ 10 MHz   | @ 10 MHz             |                   |

| GIFT                            | 1215       | 1531   | 51.8       | 51.3                 | 128     | 5248     | 27.2       | 26.9                 | this work, Sec. A |

| GIFT                            | 1213       | -      | 40.3       | -                    | 160     | 6528     | 26.3       |                      | [BPP+17]          |

| GIFT* b                         | 1108       | 1332   | 49.8       | 48.7                 | 128     | 5248     | 26.1       | 25.5                 | this work, Sec. 6 |

Table 2: The comparison of our work with the state of the art in terms of latency, area, power and energy. The measurements respect to the use of the same library and clock frequency, NanGate 45 nm and UMC 90 nm for AES, SKINNY and STM 90 nm for GIFT\*. For fair comparison, all power figures are measured at frequencies reported in the original papers [JMPS17, BPP+17]. <sup>a</sup>It has been estimated in [MPL+11] that converting a non-standardized to a standardized circuit requires an additional 20 MUXes. The area figures in this row is obtained by adding the area of 20 MUXes to the figures in the previous row. <sup>b</sup>GIFT\* refers to the slightly modified version of GIFT used in SUNDAE-GIFT [BBP+19].

assume that plaintext and the key is arranged in a row major fashion (which we call non-standard), even though the original specification of AES assumes a column-major arrangement [NIS01].

• We avoid techniques such as clock-gating, which might sometimes result in timing inconsistencies during synthesis phase and cost additional circuit area. This also brings the additional benefit of being compatible with the recently introduced glitch-resistant security model [BGI<sup>+</sup>18]. This paper provides framework for formal verification of masked designs in the presence of glitches and is thus a very useful tool to have for implementors. However, the model used in the paper assumes that all registers are triggered by a perfectly synchronized clock signal. In the case of clock-gating, this assumption does not hold, because gated clock has variable delay in comparison to the main clock source. Thus when our techniques are used to produce masked implementations by simply duplicating the combinatorial and storage circuitry, it has the added advantage of conforming to this security model, which would make it easier for the circuit designer to formally verify the security of the circuit in the presence of glitches.

In the second part of the paper, we direct our attention to implementation of four AE schemes, one for each block cipher: SUNDAE-GIFT (1201 GE), SAEAES (1350 GE), Romulus (2399 GE) and SKINNY-AEAD (3589 GE). We have chosen these candidates, because the mode of operation part of the circuit has the minimal storage requirement, thus leading to very compact implementations. To the best of our knowledge, these are the smallest block-cipher-based authenticated encryption schemes reported so far in the bit-serial and 4/8-bit-serial configurations. In Table 3, we summarize the synthesis figures for the multi-bit implementations and similarly, Table 4 tabulates the synthesis figures for our AEAD constructions under the same technology library. The measurements for other libraries can be found in Section 7.5. The source code of our implementations are also publicly available [git, c4s].

|                    | Area   | (GE)    | Power              | · (μW)               | Latency | (cycles) | Energy (nJ/128-bit) |                      |                       |

|--------------------|--------|---------|--------------------|----------------------|---------|----------|---------------------|----------------------|-----------------------|

| Block cipher       | STM 90 | UMC 180 | STM 90<br>@ 10 MHz | UMC 180<br>@ 100 KHz | round   | total    | STM 90<br>@ 10 MHz  | UMC 180<br>@ 100 KHz | Ref.                  |

| AES (standard)     | 1785   | -       | 104.5              | =                    | 16      | 176      | 1.84                | =                    | this work, Sec. 4.6   |

| AES (non-standard) | -      | 2400    | -                  | 3.7                  | 21      | 226      | -                   | 8.36                 | [MPL+11]              |

| AES (non-standard) | 2060   | -       | 130.1              | -                    | 23      | 246      | -                   | 3.2                  | [BBR17]               |

| SKINNY-128-128     | 1326   | -       | 62.4               | -                    | 16      | 656      | 4.10                | -                    | this work, Sec. 5     |

| SKINNY-128-128     | 1638   | -       | 79.1               | -                    | 21      | 840      | 6.64                | -                    | [BPP+17]              |

| SKINNY-128-128     | -      | 1840    | -                  | -                    | 21      | 872      | -                   | -                    | [BJK <sup>+</sup> 16] |

| SKINNY-128-256     | 1880   | -       | 90.5               | -                    | 16      | 784      | 7.10                | -                    | this work, Sec. 5     |

| SKINNY-128-256     | -      | 2655    | -                  | -                    | 21      | 1040     | -                   | -                    | [BJK <sup>+</sup> 16] |

| SKINNY-128-384     | 2431   | -       | 119.6              | -                    | 16      | 912      | 10.9                | -                    | this work, Sec. 5     |

| SKINNY-128-384     | -      | 3474    | -                  | -                    | 21      | 1208     | -                   | -                    | [BJK <sup>+</sup> 16] |

| GIFT <sup>a</sup>  | 1455   | -       | 79.7               | -                    | 33      | 1352     | 10.78               | -                    | [BPP+17]              |

| GIFT* b            | 1430   | -       | 61.4               | -                    | 32      | 1312     | 8.06                | -                    | this work, Sec. 6     |

Table 3: The comparison of our work with regards to 8-bit-serial AES, SKINNY and 4-bit-serial GIFT state-of-the-art implementations.  $^a$ The number of clock cycles is incorrectly reported for the 128-bit version of GIFT in [BPP+17] (and confirmed by the authors). We report the rectified figures for the respective implementation.  $^b$ GIFT\* refers to the slightly modified version of GIFT used in SUNDAE-GIFT [BBP+19].

|             |               | Area<br>(GE) | Power $(\mu W @ 10 MHz)$ | Latency (cycles) | Energy<br>(nJ/1152-bit) | Ref.     |

|-------------|---------------|--------------|--------------------------|------------------|-------------------------|----------|

| SUNDAE-GIFT | 1-bit         | 1201         | 50.1                     | 92544            | 463.6                   | Sec. 7.1 |

| SUNDAE-GIFT | 4-bit         | 1587         | 63.9                     | 23136            | 147.8                   | Sec. 7.1 |

| SAEAES      | $1	ext{-bit}$ | 1350         | 77.2                     | 24448            | 188.7                   | Sec. 7.2 |

| SAEAES      | 8-bit         | 1940         | 108.0                    | 3056             | 33.0                    | Sec. 7.2 |

| Romulus-N1  | 1-bit         | 2399         | 98.1                     | 64647            | 634.2                   | Sec. 7.3 |

| Romulus-N1  | 8-bit         | 2912         | 114.0                    | 8080             | 92.6                    | Sec. 7.3 |

| SKINNY-AEAD | 1-bit         | 3589         | 134.3                    | 72960            | 979.9                   | Sec. 7.4 |

| SKINNY-AEAD | 8-bit         | 3783         | 149.0                    | 9856             | 146.9                   | Sec. 7.4 |

Table 4: Synthesis figures for the implemented bit-serial AEAD schemes using the STM 90 nm process. Energy and throughput figures are based on the processing of 1024 bits of plaintext and 128 bits of associated data.

## 2 Preliminaries

**Notation.** We denote the set of integers  $\{a, a+1, \ldots, b\}$  with [a, b]. Furthermore, we define  $(a, b) = [a, b] \setminus \{a, b\}$ ,  $(a, b) = [a, b] \setminus \{a\}$  and  $[a, b) = [a, b] \setminus \{b\}$ . [n] is a shorthand for [0, n]. The bit string concatenation is denoted with  $|\cdot|$ .

**Pipelines.** In a circuit, a bit-serial pipeline is a series of flip-flops that are arranged in a way that allows the stored value to be shifted in a fixed direction, one bit position at each clock cycle. In mathematical terms, an n-bit pipeline can be denoted with a series of 1-bit variables  $\mathsf{FF}_0, \mathsf{FF}_1, \ldots, \mathsf{FF}_{n-1}$  that supports two main operations:  $\mathit{shift}$  and  $\mathit{swap}$ . This corresponds to flip-flops in circuit, and we simply write  $\mathsf{FF}$  to represent this series. The two operations could be better explained with the following algorithmic descriptions, which take the previous state  $\mathsf{FF}$  and returns the updated state  $\mathsf{FF}'$ :

Here, the shift operation additionally takes a new bit to be loaded into the first flip-flop  $\mathsf{FF}_{n-1}$  of the pipeline, and outputs the bit at the last flip-flop  $\mathsf{FF}_0{}^3$ . The swap operation on the other hand, which we simply refer with a tuple (u,v) hereafter, only swaps the contents of  $\mathsf{FF}_u$  and  $\mathsf{FF}_v$  without touching the other values.

What makes these two operations special is that (1) bit-sliding implementations already contain a pipeline, hence a shift operation is already available, and (2) a swap operation (u, v) can be implemented by replacing two regular flip-flops with two scan flip-flops, which brings only small cost to the circuit in terms of area footprint. However, it must be noted that u and v values must be hard coded into the swap operation, as the positions of scan flip-flops are fixed. Therefore, each distinct (u, v) swap brings extra small cost.

An interesting observation is that given any single swap operation (u, v) (with  $u \neq v$  and gcd(u-v, n) = 1) and the shift operation, one could execute an arbitrary permutation over n bits through a finite invocations of shift and swap operations, as pointed out by Banik et al. [BBRV20]. Therefore, in theory, one could implement the permutation layer of any block cipher through a single fixed swap operation, as long as the correct sequence of shift and swap calls are made by the controller circuit. However, this approach would take a large number of shift calls, hence would lead to unrealistically many number of clock cycles. A good approach therefore is to add few other swap operations to strike a balance between the circuit size and the reasonable latency.

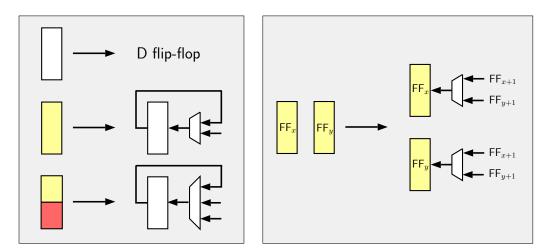

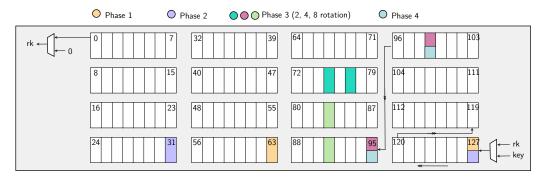

Color Coding. In the following, we make extensive use of colors to mark the swap positions in a register pipeline, as shown in Figure 1. This figure should be interpreted as a legend for the rest of the figures in this paper. Let us briefly explain the meaning of the color coding with respect to both functionality and cost. Let  $\ell_{\mathsf{FF}}$  and  $\ell_{\mathsf{MUX}}$  denote the areas of a simple flip-flop (without reset functionality) and a 2-input multiplexer respectively. As shown in Figure 1, a white box denotes a simple flip-flop and occupies area equal to  $\ell_{\mathsf{FF}}$ . Any box that contains n different colors represents a flip-flop that can accept n+1 input bits, one of which is latched on the flip-flop in the next rising clock edge, depending on some select signal. All such instances cost  $\ell_{\mathsf{FF}} + n \times \ell_{\mathsf{MUX}}$  units of silicon area (unless the technology library has a dedicated cell implementation for this primitive).

Figure 1: The color legend for interpreting circuit figures. White boxes denote a regular D flip-flop, a single-colored box is used for 2-input scan flip-flop and an n-color flip-flop denotes an (n+1)-input flip-flop. Two boxes that share a color mean that they are interconnected and therefore they can swap their input bits.

<sup>&</sup>lt;sup>3</sup>The indexing might come as counter intuitive at the first sight. However, if we load the bit sequence  $b_0, b_1, \ldots, b_{n-1}$  to the pipeline in given order, after n shift calls, each  $\mathsf{FF}_i$  stores exactly  $b_i$ .

## 3 Generic Approach

An SPN-based block cipher generally consists of three layers of operation in a round: key addition, substitution and a linear operation. The linear layer is often a combination of a permutation function and a matrix multiplication. For example in AES, the permutation function is the ShiftRows operation and matrix multiplication is done by the MixColumns operation. In the context of lightweight circuits, we can further classify these operations into 2 broad classes: (1) swap-based and (2) replacement-based. In AES, for example, the SubBytes and MixColumns operations can be seen as replacement-based operations, since they take a finite portion of the AES state and replace them with new data block of equal length. ShiftRows can be seen as a swap-based operation because it essentially swaps some bits at two different locations of the state vector. Our technique, for implementing an SPN-based block cipher, then consists of finding a good and short sequence of swap operations that corresponds to the swap-based operation, and interleave them with the replacement-based operations.

In particular, let us look at AES as an example. At the byte level, the ShiftRows is a permutation over the set [0, 15] which can be formulated as

$$(1, 13, 9, 5) \circ (2, 10) \circ (6, 14) \circ (3, 7, 11, 15)$$

Given that the AES byte order is  $b_0, b_1, \ldots, b_{15}$ , the above notation means that after ShiftRows,  $b_1$  is moved to location 13,  $b_{13}$  is moved to location 9 etc. Note that each of the k-cycles correspond to a particular row of the AES state and they commute with each other, so the order of their execution is irrelevant. The above expression can be decomposed further as

$$[(9,13)\circ(5,9)\circ(1,5)]\circ(2,10)\circ(6,14)\circ[(11,15)\circ(7,15)\circ(3,15)]$$

What does this tell us? First is that, since for all the swaps (x, y) listed above, we have  $y - x \equiv 0 \pmod{4}$ , so the permutation is special and of type 4 as per the definition by Banik et al. [BBRV20, Definition 1].

Let us turn our attention to the first 4-cycle which decomposes as  $(9,13) \circ (5,9) \circ (1,5)$  (note that these swaps no longer commute). We will show how to implement this 4-cycle in 16 clock intervals. Let us choose to implement the (11,15) swap in the circuit for this purpose, for which we place scan-flip-flop-based byte registers in locations 10 and 14 as shown in Figure 2. The only reason we chose these locations was that they are 4 places apart. Later it would be easy to see that we could have chosen any 2 locations (x, x + 4) for this purpose.

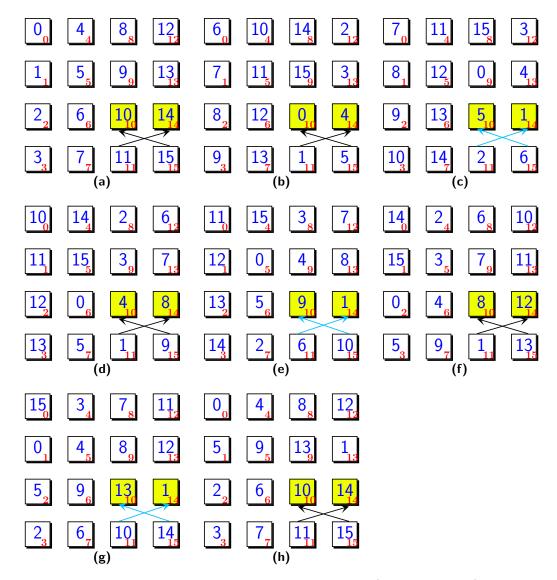

The first task is to execute (1,5). We do the rotate operation, denoted by r, a total of 6 times on the circuit, and so that bits arrive to positions shown in Figure 2(b). We now invoke the scan functionality so that in the next cycle bytes 1, 5 would be in positions 10 and 14 as shown in Figure 2(c). Note that in doing so we effectively execute the permutation  $\theta = r \circ (11, 15)$ . The next swap to be executed is (5, 9), which corresponds to  $b_1 \leftrightarrow b_9$  in the current state. By rotating 3 more times, we reach to the state in Figure 2(d), where the bytes  $b_1$ ,  $b_9$  are in place to be swapped in the next cycle. After executing  $\theta$  at this point, we reach to the state in Figure 2(e). The final swap to be performed is (9,13), which as per the previous logic is swapping bytes  $b_1 \leftrightarrow b_{13}$ . Again it is easy to see that performing  $\theta \circ r^3$  over the next 4 cycles gives us the position in Figure 2(g), where all the bytes have now been swapped as required. We perform the rotate operation once more to get the position in Figure 2(h), where all bytes are back to the original position and the ShiftRows operation has been executed on the 1st row. In effect the permutation we performed is  $r \circ \theta \circ r^3 \circ \theta \circ r^3 \circ \theta \circ r^6$ , which takes 16 cycles. Note that if we had chosen any other swap location of the form (x, x + 4), it would still be possible to do the above sequence of operations. For example if we had chosen the swap (9,13) instead of (11,15),

Figure 2: The contents of pipeline (a) initially, (b) after  $r^6$ , (c) after  $\theta \circ r^6$ , (d) after  $r^3 \circ \theta \circ r^6$ , (e) after  $\theta \circ r^3 \circ \theta \circ r^6$ , (f) after  $r^3 \circ \theta \circ r^3 \circ \theta \circ r^6$ , (g) after  $\theta \circ r^3 \circ \theta \circ r^3 \circ \theta \circ r^6$ , (g) finally after  $r \circ \theta \circ r^3 \circ \theta \circ r^3 \circ \theta \circ r^6$ . Note the numbers in blue denote the byte index, i.e corresponds to  $b_i$ , and the subscripts in red denote the fixed register positions. As explained in Figure 1, the yellow boxes denote the byte registers implemented with scan flip-flops. Cyan and black arrows denote whether the operation  $\theta$  or r is executed respectively.

we would need to execute  $\theta' \circ r^3 \circ \theta' \circ r^3 \circ \theta' \circ r^8$ , where  $\theta' = r \circ (9, 13)$ . This already takes 17 cycles and so all the bytes will be indeed swapped correctly, but not return to their original positions as before. Conceptually this means that if the AES round is executed in 16 cycles, then a few of the swap operations of the current round would take place in the next round, and we would have to tailor the other operations in the pipeline accordingly.

Following the same logic, let us now try to do the swaps  $(2,10) \circ (6,14)$  of the next row. This time, let us choose two swap locations 8 places apart, in particular (5,13). The above swaps commute and so can be done in any order, so let us do (2,6) first. After  $r^{13}$ , the bytes  $b_2$ ,  $b_6$  are in place for swapping, and in the next cycle we execute the scan functionality to perform  $\alpha = r \circ (5,13)$ . After 3 more cycles of r, the bytes  $b_6$ ,  $b_{14}$  are in place, and then we execute  $\alpha$  again. Thus by executing  $\alpha \circ r^3 \circ \alpha \circ r^{13}$ , we have again already spent 18 cycles. As explained before, this indicates that at this point, the bytes have again been correctly swapped in terms of their relative order in the pipeline and that in terms of data flow in the circuit, some of the swaps of the current AES round overflow into the next round.

The third set of swaps for the final row is  $(11, 15) \circ (7, 15) \circ (3, 15)$ . We can construct this sequence with 3 different swap locations also at distances 4, 8 and 12 apart. Let us choose the swaps (11, 15), (5, 13) as before and (2, 14) as the additional swap location. We have to execute (3, 15) first, therefore we rotate once to bring the bytes  $b_3$  and  $b_{15}$  in place and then execute  $\beta = r \circ (2, 14)$ . We will now use the swap locations (11, 15), (5, 13), which have already been used to do swaps in the previous 2 rows. At this point  $b_7$  and after the previous swap  $b_3$  are already in place and so we execute  $\alpha$  on the location (5, 13) by invoking its scan functionality. For the last remaining swap (11, 15), we have to wait till  $b_{11}$  returns to location 11, which requires 13 more rotations after which we can invoke  $\theta$ .

**Putting it together.** We have just put together a set of swap sequences that enable the execution of the AES ShiftRows operation. We looked at each row separately and so it is conceivable that the swap sequences be performed one after the other, thereby requiring a little over 48 cycles. But in the interest of latency, we wish to do them in 16 and if required within a few cycles of the next round. Since the k-cycles in each row that we executed commute with each other, the swaps can actually be executed concurrently. That is, following the above example, we

- 1. invoke scan functionality on the swap location (2,14) at clock cycle 1 (assuming we start with cycle 0);

- 2. invoke scan functionality on the swap location (5, 13) at clock cycles 2, 13, 17;

- 3. invoke scan functionality on the swap location (11, 15) at cycle 6, 10, 14, 16.

The point is that since the k-cycles commute, we execute the swaps concurrently on the given locations in 18 continuous cycles (numbered 0 to 17) and still achieve the ShiftRows functionality (this roughly follows from [BBRV20, Lemma 7]). Indeed it is a matter of a simple arithmetic exercise to see that the arrangement of bytes obtained after executing the above sequence of swaps concurrently in 18 cycles results in ShiftRows off by 2 extra rotations.

We have seen that we can execute AES ShiftRows and more generally any permutation of type 4, by judiciously choosing swap locations at distances 4, 8, 12 and tailoring the swap sequences around it. What about the other operations like SubBytes and MixColumns? That is where the engineering challenge lies. Since these are substitution type operations, they have to be accommodated in the pipeline preferably when the scan functionalities of the registers are not being invoked. There are of course precedence issues a designer would have to deal with, for example, the SubBytes and ShiftRows in any round must precede the MixColumns. Can this technique be applied to other block ciphers in general? For block ciphers that employ some kind of byte/nibble/word-based swap operations in their

permutation function, the answer is affirmative. For example, SKINNY has a permutation function given by

$$(4,5,6,7) \circ (9,11) \circ (8,10) \circ (12,15,14,13).$$

This is a permutation of type 1, and has a similar form with AES, so it takes modest effort to construct it using swaps, in the same fashion explained above. For block ciphers such as GIFT that employ bit-based permutation function, the technique becomes slightly more involved.

From byte to bit-serial. When we reduce the datapath to 1 bit, we can no longer swap 2 bytes in one cycle and it would take exactly 8 cycles for every byte swap. At the bit level, ShiftRows of AES is essentially the composition of the following permutations over the set [0, 127] for all  $k \in [0, 7]$ :

```

(8+k, 104+k, 72+k, 40+k) \circ (16+k, 80+k) \circ (48+k, 112+k) \circ (24+k, 56+k, 88+k, 120+k)

```

As it can be seen from this expansion, at the bit level, everything scales by a factor of 8. At the byte level, we used the sequence  $r \circ \theta \circ r^3 \circ \theta \circ r^3 \circ \theta \circ r^6$  to execute 4-cycle (1, 13, 9, 5) with the swap located at (11, 15). At the bit level, let us choose the swap locations (88, 120), located 32 places apart. Using the same logic as before, it is easy to see that  $r^8 \circ \theta_1^8 \circ r^{24} \circ \theta_1^8 \circ r^{24} \circ \theta_1^8 \circ r^{48}$  can realize  $\bigcup_{k=0}^7 (8+k,104+k,72+k,40+k)$ , where  $\theta_1 = (88,120) \circ r$  (with  $\bigcup$  denoting the composition operation). Similarly by choosing swap locations that are 64 and 96 places apart, we can permute the other rows using the same multiplicity by 8 principle. Similarly the SKINNY permutations can be designed for the bit-serial datapath with swap locations 8, 16 and 24 places apart.

### 4 AES

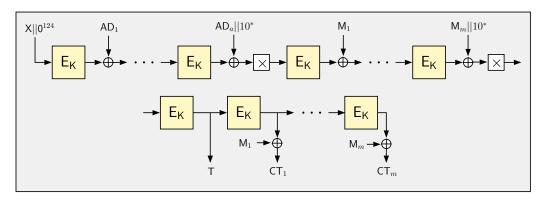

For the rest of this section, we assume familiarity with the round function and the key scheduling algorithms of AES [NIS01]. Our circuit simply consists of the following circuits in the main hierarchy: (1) a state pipeline, (2) a key pipeline, (3) a controller, (4) a shared S-box.

#### 4.1 State Pipeline

The state in our design uses the following components/techniques:

- nibble-level MixColumns circuit introduced by Jean et al. [JMPS17],

- the smallest known AES S-box "bonus" from Maximov and Ekdahl [ME19].

Given that state and key bits are stored in a pipelined fashion, one can easily notice that AddRoundKey can be performed without much hassle as long as each of the state and key pipelines produces the correct bit per clock cycle. Hence, the main challenges on the state pipeline part is to (1) execute all SubBytes, ShiftRows, MixColumns operations simultaneously, (2) complete the operations in 128 clock cycles, while (3) following the standard ordering of bits for the plaintext and the key. Below, we first describe each layer separately, and show how we can fuse them into one operation that executes over the state pipeline continuously.

#### 4.2 ShiftRows with Swaps

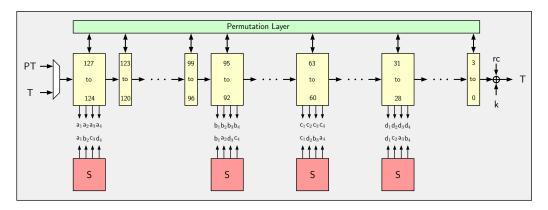

Assume that the 128-bit pipeline is defined in the same fashion as in Section 2, i.e. the bits are loaded into  $\mathsf{FF}_{127}$  and they are flushed out by  $\mathsf{FF}_0$ . We use three swap operations to execute the ShiftRows layer: (80,112), (56,120) and (25,121). The timetable for scheduling

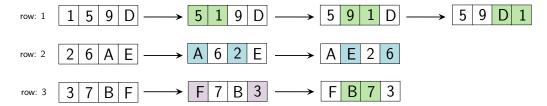

Figure 3: The transition diagram for rows 1, 2, 3; where the colored cells denote the recently modified values. Note that there are three distinct swap operations, with distance 0, 1 and 2 cells in-between.

these swaps are given in Table 5. Below, we explain how we came up with these swap sequences and the mechanism in which they work for shifting rows correctly.

For simplicity, let us forget about the pipeline and shift operations for the moment, and focus on the nature of ShiftRows in the 16-byte state. We try to express ShiftRows in terms of byte swaps. Suppose that the values contained in the state are the hexadecimal characters  $0, 1, \ldots, F$ . Considering the standard byte arrangement for loading the initial data [NIS01], row 0 contains the values 0, 4, 8, C; row 1 contains the values 1, 5, 9, D etc. We then devise a sequence of swap operations over the rows 1, 2, 3 to perform ShiftRows. Our three distinct swaps are denoted with distinct colors in Figure 3. This figure shows the movement of the bytes as they arrive to their final position implied by ShiftRows.

We point out two important observations: (1) each byte-swap operation can be executed by a bit-swap circuit through 8 consecutive calls interleaved by shift operations, (2) the swap operations denoted with the same color can actually be executed by a single swap operation as long as it is enabled in the correct clock cycle. Therefore, the choice of swaps and the timetable in Table 5 are straightforward extensions of this example into the 128-bit state pipeline.

| pipeline | operation      | active cycles                                     |

|----------|----------------|---------------------------------------------------|

| state    | swap (80, 112) | $[56,64) \cup [88,96) \cup [120,127] \cup [8,16)$ |

|          | swap (56, 120) | $[88, 96) \cup [120, 127] \cup [0, 8)$            |

|          | swap (25, 121) | $\{127\} \cup [0,6]$                              |

|          | load S-box     | $\{8k+7: k \in [0,15]\}$                          |

|          | load Mix Col.  | $[32,40) \cup [64,72) \cup [96,104) \cup [0,8)$   |

| key      | swap (96, 128) | [0,8)                                             |

|          | swap (40, 72)  | [56, 64)                                          |

|          | load S-box     | $\{112\} \cup \{120\} \cup \{0\} \cup \{8\}$      |

|          | key XOR        | [0, 96)                                           |

|          | add RC         | (lookup table)                                    |

Table 5: The timetable of operations for bit-serial AES encryption.

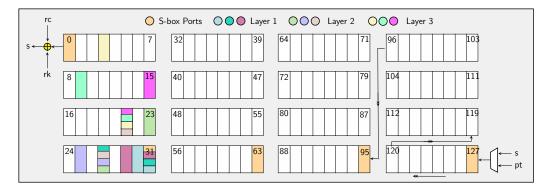

To help understand how the structure helps perform the ShiftRows operation, we note that since the pipeline is always active, the shift operation is performed in every clock cycle. To additionally perform the swap  $80 \leftrightarrow 112$ , in any clock cycle, we need to place scan flip-flops at locations 79 and 111 (and wire the output of 80 to the input of 111; wire the output of 112 to the input of 79) as is shown in Figure 4. So assuming that the bits indexed 0 to 127 enter the pipelines through the location 127, at clock cycle  $k \leq 127$ , the pipeline stores exactly k bits. For instance, in the 56-th clock cycle, the bits indexed 8, 40 are at locations 80, 112 respectively. Enabling swaps for cycles 56 to 63 therefore swaps bits  $8, \ldots, 15$  with  $40, \ldots, 47$ , which are essentially bytes indexed by 1 and 5. It can be

verified without difficulty that performing the same swap in cycles [88,96) actually swaps bytes 1 and 9. This exactly follows the explanation in Section 3 using (80,112) as swap locations instead of (88,120). Similarly the same swap in cycles [120,127) swaps bytes 1 with 13, which completes the ShiftRows operation on row 1. It is not too difficult to verify that the other swaps at cycles as listed in Table 3 faithfully perform the remaining ShiftRows operations.

#### 4.3 The Nibble MixColumns

The nibble MixColumns was introduced by Jean et al. [JMPS17]. The multiplication over a single column is completed over 8 clock cycles, updating each nibble at a time. To simplify, we first represent a single column of bytes as 8 vertical nibble vectors as below. Namely, from the pipeline given in Figure 4, the vectors  $M_i$  are defined for  $0 \le i \le 7$  as below:

$$M_i := \begin{bmatrix} \mathsf{FF}_i \\ \mathsf{FF}_{i+8} \\ \mathsf{FF}_{i+16} \\ \mathsf{FF}_{i+24} \end{bmatrix} \qquad \qquad \mathcal{R}(M_0) := \begin{bmatrix} \mathsf{FF}_8 \\ \mathsf{FF}_{16} \\ \mathsf{FF}_{24} \\ \mathsf{FF}_0 \end{bmatrix}$$

The nibble MixColumns architecture employs an additional set of 4 flip-flops to help with the serialized computation of this functionality. Define the vector  $M_8$  to denote this additional internal 4-bit storage this architecture employs. During its 8 clock cycle operation, these flip-flops are used to keep the value of the leftmost bit of each one of the four bytes. We define a function upward rotation  $\mathcal{R}$  that rotates the elements in a given vertical matrix by one position, as exemplified above. The circuit essentially performs the following sequence of operations to derive the new value of  $M_i$  for each  $i=0,1,\ldots,7$ , starting from i=0 respectively:

- if i = 0, store  $M_8 \leftarrow M_0$  before any of the following computation,

- update  $M_i \leftarrow \mathcal{R}(M_i) \oplus \mathcal{R}^2(M_i) \oplus \mathcal{R}^3(M_i) \oplus M_{i+1} \oplus \mathcal{R}(M_{i+1}),$

- if  $i \in \{3, 4, 6\}$ , further update  $M_i \leftarrow M_i \oplus M_8 \oplus \mathcal{R}(M_8)$ .

In other words, at each clock cycle, based on the internal 7-bit counter, we can execute a single slice of the previous computation. In total, it takes 8 clock cycles for a single column, and 32 clock cycles for the whole MixColumns layer. This serial circuit can be realized with 8 XOR, 8 NAND gates and 4 flip-flops (see Figure 1 of [JMPS17]).

#### 4.4 Combined State Pipeline

In the controller, the circuit contains an 11-bit counter to keep both the round (4-bit) and the phase (7-bit). We split this counter into two parts and refer to them respectively by variables  $0 \le \text{round} \le 10$  for the upper 4-bit and  $0 \le \text{count} \le 127$  for the lower 7-bit.

In contrast to previous work [JMPS17], we follow the standard ordering of bits in our implementation. That is given a plaintext and a key, the bits are loaded into the circuit starting from the leftmost bits, and following the natural order [NIS01]. This becomes a crucial aspect of a block cipher implementation, if it is meant to be used in a mode of operation that needs to comply with a fixed standard.

At the beginning of its operation, the 11-bit counter is reset to zero. During initialization, i.e.  $\mathsf{round} = 0$ , the white-colored MUXes in Figure 4 are configured so that the next bit s of the state is received from the input port PT but after the XOR is performed with KEY, which is also being loaded at the same time. For  $\mathsf{round} > 0$ , we select the state bit to be loaded from the exit of the state pipeline.

Figure 4: The state (above) and key (below) pipelines of AES-128 encryption with colored scan flip-flops. S-box output ports are denoted with  $S_0||S_1||\dots||S_7$ .

**SubBytes.** Meanwhile, we proceed with executing the SubBytes layer, by enabling the S-box at every 8-th cycle. More precisely, the S-box is configured to take  $\mathsf{FF}_{121}, \mathsf{FF}_{122}, \ldots, \mathsf{FF}_{127}$  and s as input, and the scan flip-flops  $\mathsf{FF}_{120}, \ldots, \mathsf{FF}_{127}$  are instructed to load the output from the S-box if count mod s = 7.

**ShiftRows.** Starting from count = 56, the swap operations become active. Many of the bits need to make a couple of jumps before they are located into their ultimate positions implied by ShiftRows, as demonstrated in Figure 3. Hence, position-wise, many bits are incorrectly located and look garbled as they pass through flip-flops  $\mathsf{FF}_{24}, \ldots, \mathsf{FF}_{120}$ . Nonetheless, as soon as they exit the last swap position  $\mathsf{FF}_{24}$ , they are guaranteed to be in their final position. See Table 5 to notice that the last swap operation executed on a layer actually happens when  $\mathsf{count} = 15$  in the next round. In other words, performing ShiftRows over the i-th state uses the last 72 cycles of the round i and the first 16 cycles of the round i+1, and it is not aligned with the counter round itself.

**MixColumns.** The input ports to the nibble MixColumns circuit are flip-flops  $\mathsf{FF}_i$  for  $i \in \{0, 1, 8, 9, 16, 17, 24, 25\}$ , and the output ports are input to the exit MUX of the pipeline and  $\mathsf{FF}_7, \mathsf{FF}_{15}, \mathsf{FF}_{23}$  respectively. The MixColumns of round i is performed at round  $i \in \mathsf{FF}_7, \mathsf{FF}_{15}, \mathsf{FF}_{23}$  respectively. The MixColumns of round  $i \in \mathsf{FF}_7, \mathsf{FF}_{15}, \mathsf{FF}_{23}$  respectively. The MixColumns of round  $i \in \mathsf{FF}_7, \mathsf{$

Resolving overlaps. Note that there are two clock cycles, i.e. count values, during which two operations modify the same FF simultaneously in Table 5. First, at clock cycle 127 both S-box and swap (25, 121) attempts to overwrite  $FF_{120}$ . Here, the operation precedence is given to the S-box (as SubBytes comes before ShiftRows), meaning that the leftmost output bit of the S-box is fed to the swap operation (instead of  $FF_{120}$ ). A second overlap occurs when count = 3, as MixColumns circuit attempts to read  $FF_{25}$  before its value is updated correctly by the swap (25, 121). Here, the precedence is given to the swap operations, meaning that the output of the swap operation is fed as input to MixColumns

circuit (instead of  $FF_{25}$ ).

## 4.5 Key Pipeline

Suppose that  $K_0, K_1, \ldots, K_{15}$  represent the key bytes of a particular round. Then the next round key sequence  $K_{16}, \ldots, K_{31}$  is computed as follows:

$$\begin{bmatrix} K_{16} & K_{20} & K_{24} & K_{28} \\ K_{17} & K_{21} & K_{25} & K_{29} \\ K_{18} & K_{22} & K_{26} & K_{30} \\ K_{19} & K_{23} & K_{27} & K_{31} \end{bmatrix} \leftarrow \begin{bmatrix} K_{0} & K_{4} & K_{8} & K_{12} \\ K_{1} & K_{5} & K_{9} & K_{13} \\ K_{2} & K_{6} & K_{10} & K_{14} \\ K_{3} & K_{7} & K_{11} & K_{15} \end{bmatrix} \oplus \begin{bmatrix} \mathsf{S}(K_{13}) \oplus \mathsf{RC} & K_{16} & K_{20} & K_{24} \\ \mathsf{S}(K_{14}) & K_{17} & K_{21} & K_{25} \\ \mathsf{S}(K_{15}) & K_{18} & K_{22} & K_{26} \\ \mathsf{S}(K_{12}) & K_{19} & K_{23} & K_{27} \end{bmatrix}$$

where RC denotes the round constant byte.

In summary, the first column requires special treatment, because it involves S-box calls, and the remaining three columns can be updated smoothly (by simply XORing with a neighboring bytes). In particular, one can notice the disarrangement in the update of the first column, as it takes the current last columns bytes with a downward rotation (by one byte). If we implement this in a straightforward fashion by updating each byte when they arrive to position 0, we would have to choose the input of the S-box either from the position 13 (for computing  $K_{16}$ ,  $K_{17}$ ,  $K_{18}$ ) or 9 (for computing  $K_{19}$ ). This means that we would have to put an extra 8-bit MUX to choose which value needs to be fed to the S-box. Instead, we decided to temporarily move the byte  $K_{12}$  to position 13 before it is fed to S-box, and then return back to its original position after the S-box operation is done. Therefore the pipeline performs the following operations in sequence:

- In the first 8 clock cycles, we activate the swap (96, 128) so that the key byte  $K_{12}$  is temporarily moved such that it comes after  $K_{15}$ . Here,  $\mathsf{FF}_{128}$  actually refers to the new key bit that is about to be loaded into the key pipeline. With this operation, the key pipeline contains  $K_{13}$ ,  $K_{14}$ ,  $K_{15}$ ,  $K_{12}$ , in given order. Hence, it respects the order they are being used to update the first key column.

- In clock cycles 112, 120 (of the current round) and 0, 8 (of the next round); the S-box is used by the key pipeline. During these cycles, the S-box reads  $K_{13}$ ,  $K_{14}$ ,  $K_{15}$ ,  $K_{12}$  from  $\mathsf{FF}_{120},\ldots,\mathsf{FF}_{127}$  in given order. The output from the S-box is XORed with  $\mathsf{FF}_{16},\ldots,\mathsf{FF}_{23}$  and the result is loaded into  $\mathsf{FF}_{15},\ldots,\mathsf{FF}_{22}$ .

- The round constant is added as the bit FF<sub>24</sub> is loaded into FF<sub>23</sub>. We use a lookup table to decide when the round constant bit is enabled. In total, this bit is enabled 16 times during the whole encryption.

- During the clock cycles [56, 64), we activate the swap (40, 72) to return  $K_{12}$  back to its original relative position. Hence the internal ordering of the bytes becomes  $K_{12}$ ,  $K_{13}$ ,  $K_{14}$ ,  $K_{15}$  again.

- For the rest of the key bits, we handle the key scheduling by activating  $\mathsf{FF}_{31} \leftarrow \mathsf{FF}_0 \oplus \mathsf{FF}_{32}$  during the clock cycles [0,96).

Table 6 tabulates the synthesis results for this AES circuit under 5 different standard cell libraries.

#### 4.6 8-bit Datapath

As already stated, there are several implementations of AES with a byte-serial datapath that can execute one AES round in 21 cycles [MPL<sup>+</sup>11, BBR16]. Since it is not possible to implement the circuit in less than 20 cycles if the number of S-boxes is limited to one, this represents a close-to-optimal latency for this datapath. However, note that these two circuits adopt a non-standard, row first arrangement of bytes. One of our goals therefore

| Library                  | Are         | a     | Power $(\mu W)$ | Latency | (cycles) | Energy       | Throughput |

|--------------------------|-------------|-------|-----------------|---------|----------|--------------|------------|

|                          | $(\mu m^2)$ | (GE)  | @ 10 MHz        | round   | total    | (nJ/128-bit) | (Mbit/s)   |

|                          |             | 1-bit |                 | t       |          |              |            |

| STM 90 nm                | 5562.6      | 1267  | 73.6            | 128     | 1408     | 10.4         | 13.44      |

| UMC 90 nm                | 5016.8      | 1600  | 65.2            | 128     | 1408     | 9.2          | 12.53      |

| TSMC 90 nm               | 4692.2      | 1663  | 56.1            | 128     | 1408     | 7.9          | 14.50      |

| NanGate 15 nm            | 441.8       | 2247  | 18.4            | 128     | 1408     | 2.6          | 293.89     |

| NanGate $45~\mathrm{nm}$ | 1575        | 1974  | 143             | 128     | 1408     | 20.1         | 45.87      |

|                          |             |       | 8-bi            | t       |          |              |            |

| STM 90 nm                | 7838.0      | 1785  | 104.5           | 16      | 176      | 1.84         | 112.96     |

| UMC 90 nm                | 6917.2      | 2206  | 85.6            | 16      | 176      | 1.51         | 115.60     |

| TSMC 90 nm               | 6361.0.2    | 2256  | 68.9            | 16      | 176      | 1.21         | 121.89     |

| NanGate 15 nm $$         | 564.2       | 2870  | 23.1            | 16      | 176      | 0.42         | 2160.68    |

| NanGate 45 nm $$         | 2022.9      | 2535  | 192.4           | 16      | 176      | 3.38         | 376.94     |

Table 6: Synthesis figures for the AES-128 encryption-only circuits.

was to design a circuit that uses standard byte ordering. Since there already exists a 21-cycles-per-round circuit that achieves close to optimal latency, we did not attempt to design one that also achieves 20 cycles per round. Instead, we focus on an implementation that closely matches our bit-serial circuit, and achieves one round in 16 cycles, by using 2 S-box circuits<sup>4</sup>.

Since this circuit closely resembles the bit-serial circuit, all the calculations of swap locations and the time intervals when the swap functionality is invoked basically scale by a factor of 8. It is best to summarize it using the following salient points:

- The circuit has 32 byte-registers Reg<sub>0</sub> to Reg<sub>15</sub> and Key<sub>0</sub> to Key<sub>15</sub>, and we use the following swap operations to implement ShiftRows: (a) (9,13) in cycles 7, 11, 15, 0, (b) (6,14) in cycles 11, 15, 0, and (c) (2,14) in cycle 0.

- We use a {0,1}<sup>32</sup> → {0,1}<sup>32</sup> MixColumns circuit for this implementation. We chose to use the MixColumns implementation with 92 XOR gates from Maximov [Max19], which has the lowest gate count known in the literature. The operation is performed in cycles 0, 4, 8, 12. The inputs are taken from the byte registers in the first column and written in registers 1, 2, 3, 15 in the order from MSB to LSB. This closely resembles the bit-serial circuit.

- The key addition and S-box are done in every cycle.

- The key pipeline uses the swaps (11, 15) in cycle 0 and (4,8) in cycle 7. The column addition in the key update is done by calculating  $\mathsf{Key}_3 \leftarrow \mathsf{Key}_0 \oplus \mathsf{Key}_4$ , in cycles 0 to

Table 6 tabulates the synthesis results for the 8-bit circuit for the same 5 different standard cell libraries.

#### 5 SKINNY

SKINNY provides six different variants [BJK<sup>+</sup>16]. In this paper, we consider the variants that are used by NIST LWC candidates, i.e. these are the members with 128-bit block

<sup>&</sup>lt;sup>4</sup>Note that theoretically, it ought to be possible to implement an AES round in 10 cycles with 2 S-boxes, but we found that it would be difficult to design a pipeline for such a circuit using low gate count. Such implementation would require many multiplexers to arrange the component operations in place and would increase the area significantly.

| pipeline      | operation       | active cycles                                          |

|---------------|-----------------|--------------------------------------------------------|

| state         | swap (112, 120) | $[112, 120) \cup [120, 127] \cup [0, 8) \cup [64, 72)$ |

|               | swap (104, 120) | $[64,72) \cup [88,96) \cup [96,104)$                   |

|               | swap (96, 120)  | [64, 72)                                               |

|               | load S-box      | $\{8k: k \in [0, 15]\}$                                |

|               | rc addition.    | (lookup table + LFSR)                                  |

|               | load Mix Col.   | [0, 32)                                                |

| tweakey 1,2,3 | swap (56, 120)  | $[72, 127] \cup [0, 8)$                                |

|               | swap (48, 56)   | [120, 127]                                             |

|               | swap (24, 56)   | $[112, 120) \cup [120, 127] \cup [0, 8)$               |

|               | swap (8, 24)    | $[120, 127] \cup [0, 8) \cup [24, 32)$                 |

| tweakey 2     | swap (0, 1)     |                                                        |

|               | LFSR XOR        | $\{8k: k \in [0,7]\}$                                  |

| tweakey 3     | LFSR (8-bit)    | $\{8k: k \in [0,7]\}$                                  |

Table 7: The timetable of operations for bit-serial SKINNY-128-384 encryption circuit.

size, as given in Table 1. In these variants, the tweakey size is variable, i.e. it can consists of 128z bits for z=1,2,3. For the remainder of the paper, we refer to these three versions by SKINNY-128-128, SKINNY-128-256 and SKINNY-128-384 respectively.

SKINNY is quite similar to AES in design, but it employs more lightweight operations for the round function. Prominently, S-box and MixColumns can be realized with much smaller circuitry compared to AES. The round function consists of SubCells, AddConstants, AddRoundTweakey, ShiftRows, MixColumns. For the finer details of these layers, we refer the reader to the original SKINNY paper  $[BJK^+16]$ .

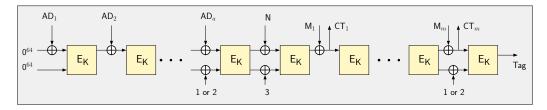

Our design follows a similar architecture to that of AES. The circuit simply consists of the following parts in the main hierarchy: (1) a state pipeline (which includes a dedicated S-box), (2) a key pipeline, (3) a controller. Below, we will explain the 1-bit implementation, and modifying the circuit into 8-bit implementation is quite straightforward.

#### 5.1 Combined State Pipeline

In the controller, the circuit contains an 13-bit counter to keep both the round (6-bit) and the phase (7-bit). We split this counter into two parts and refer to them respectively by variables  $0 \le \text{round} \le 56$  for the upper 4-bit and  $0 \le \text{count} \le 127$  for the lower 7-bit.

Because SKINNY is already designed with hardware-friendliness in mind, we load the bits into the circuit starting from the leftmost bits, by following the standard  $[BJK^+16]$ . In our implementations the key blocks and the plaintext are loaded simultaneously and completed in 128 cycles. This applies to all three versions of SKINNY-128-128, SKINNY-128-256, SKINNY-128-384.

At the beginning of its operation, the 13-bit counter is reset to zero. Then during initialization, i.e. round = 0, the plaintext is loaded through 1-bit input port, and the key is loaded through z-bit input port into their respective pipelines without modification. Each tweakey block has its own dedicated input port. These ports are denoted with PT (for plaintext) and KEY1, KEY2, KEY3 for the tweakey. Below, we describe the layers of operations executed on the state pipeline, in an order observed by the incoming bits.

**SubCells.** SubCells layer is executed by enabling the S-box at every 8-th cycle. More precisely, the S-box is configured to read  $\mathsf{FF}_{120}, \mathsf{FF}_{121}, \ldots, \mathsf{FF}_{127}$  as input, and the scan flip-flops  $\mathsf{FF}_{119}, \ldots, \mathsf{FF}_{126}$  are instructed to be loaded with the S-box output if **count** mod 8=0.

AddConstants. The round constants are added right after the S-box operation. An XOR gate is placed between  $\mathsf{FF}_{119}$  and  $\mathsf{FF}_{120}$ , and the round constant bit  $\mathit{rc}$  is added. We

Figure 5: The state (above) and key ( $TK1,\,TK2$  and TK3 respectively) pipelines of SKINNY encryption.

use a 7-bit LFSR circuit (not shown in the figure) to produce the round constant bit.

**AddRoundTweakey.** The key bits are added at the same position with the round constant bit, i.e. between  $\mathsf{FF}_{119}$  and  $\mathsf{FF}_{120}$ . In order to synchronize this with the key pipeline, the key bits  $k_0, k_1, k_2$  are read from  $\mathsf{FF}_{120}$  of the key pipeline. The key addition is active during  $8 \leq \mathsf{count} < 72$ . This corresponds to adding the first half of each tweakey.

**ShiftRows.** This layer is executed with 3 swap operations, similar to AES, and the timetable of swaps are given in Table 7. Position-wise, bits are incorrectly located and look garbled as they pass through flip-flops  $\mathsf{FF}_{95},\ldots,\mathsf{FF}_{119}$ , but as soon as they exit the last swap position  $\mathsf{FF}_{95}$ , they are guaranteed to be in their final position.

**MixColumns.** The input ports to the nibble MixColumns circuit are flip-flops  $\mathsf{FF}_i$  for  $i \in \{0, 32, 64, 96\}$ , and the output ports are input to the exit MUX of the pipeline and  $\mathsf{FF}_{31}, \mathsf{FF}_{63}, \mathsf{FF}_{95}$  respectively. The MixColumns is active during the first 32 clock cycles of a round.

**Resolving overlaps.** Note that during clock cycles  $64 \le \text{count} < 72$  three swaps (112, 120), (104, 120), (96, 120) are active at the same time and overlap at the same flip-flop  $\mathsf{FF}_{120}$ . The order of execution here is (96, 120), (104, 120) and (112, 120) respectively.

#### 5.2 Key Pipeline

SKINNY can have up to three blocks of tweakey, referred to as TK1, TK2, TK3 [BJK<sup>+</sup>16]. The key schedule algorithm is quite similar in all three key blocks. More precisely, suppose that  $K_0, K_1, \ldots, K_{15}$  represent the key bytes of a particular tweakey block. Then the next round key sequence  $K_{16}, \ldots, K_{31}$  is computed as follows:

$$\begin{bmatrix} K_{16} & K_{17} & K_{18} & K_{19} \\ K_{20} & K_{21} & K_{22} & K_{23} \\ K_{24} & K_{25} & K_{26} & K_{27} \\ K_{28} & K_{29} & K_{30} & K_{31} \end{bmatrix} \leftarrow \begin{bmatrix} \mathcal{L}_i(K_9) & \mathcal{L}_i(K_{15}) & \mathcal{L}_i(K_8) & \mathcal{L}_i(K_{13}) \\ \mathcal{L}_i(K_{10}) & \mathcal{L}_i(K_{14}) & \mathcal{L}_i(K_{12}) & \mathcal{L}_i(K_{11}) \\ K_0 & K_1 & K_2 & K_3 \\ K_4 & K_5 & K_6 & K_7 \end{bmatrix}$$

where the operation  $\mathcal{L}_i$  are 8-bit permutations given below:

$$\mathcal{L}_{1}(x_{7}||x_{6}||x_{5}||x_{4}||x_{3}||x_{2}||x_{1}||x_{0}) := x_{7}||x_{6}||x_{5}||x_{4}||x_{3}||x_{2}||x_{1}||x_{0}$$

$$\mathcal{L}_{2}(x_{7}||x_{6}||x_{5}||x_{4}||x_{3}||x_{2}||x_{1}||x_{0}) := x_{6}||x_{5}||x_{4}||x_{3}||x_{2}||x_{1}||x_{0}||(x_{7} \oplus x_{5})$$

$$\mathcal{L}_{3}(x_{7}||x_{6}||x_{5}||x_{4}||x_{3}||x_{2}||x_{1}||x_{0}) := (x_{0} \oplus x_{6})||x_{7}||x_{6}||x_{5}||x_{4}||x_{3}||x_{2}||x_{1}|$$

Therefore, our key pipelines do the following operations in sequence. First, we swap the first and the last eight bytes by using the swap (56, 120). Then we perform the local byte permutations on the upper half (i.e. the first 8 bytes) of the key through swaps (48, 56), (24, 56), (8, 24). Finally we apply the 8-bit permutation  $\mathcal{L}_2$  through another swap (0, 1) for TK2, and a dedicated 8-bit LFSR circuit for  $\mathcal{L}_3$  in TK3.

The 8-bit implementation is in fact simpler than 1-bit, because circuitry such as LFSR, S-box are already compatible with the datapath size. We only need to add extra gates for swaps, e.g. extend each single swap into byte swap, and duplicate circuit for MixColumns. The timetable is also updated so that each consecutive activity in 8 clock cycles are squeezed into one. Table 8 tabulates the synthesis results for the 1/8-bit circuit for 5 different standard cell libraries.

## 6 GIFT\*

We will be focusing our efforts on the bit-sliced design of the GIFT block cipher, as utilized in the NIST LWC candidates GIFT-COFB and SUNDAE-GIFT [BCI+19, BBP+19]. We denote it by GIFT\* as it differs from the original construction in the way data bits are

| Library             | Are $(\mu m^2)$ | ea<br>(GE) | Power $(\mu W)$<br>@ 10 MHz | Latency<br>round | (cycles)<br>total | Energy (nJ/128-bit) | Throughput<br>(Mbit/s) |