# Spectre Declassified: Reading from the Right Place at the Wrong Time

```

Basavesh Ammanaghatta Shivakumar , Jack Barnes , Gilles Barthe , Sunjay Cauligi , Chitchanok Chuengsatiansup , Daniel Genkin Sioli O'Connell , Peter Schwabe , Rui Qi Sim , Yuval Yarom Georgia Institute of Technology, Atlanta, United States IMDEA Software Institute, Madrid, Spain MPI-SP, Bochum, Germany Radboud University, Nijmegen, The Netherlands The University of Adelaide, Adelaide, Australia

```

Abstract—Practical information-flow programming languages commonly allow controlled leakage via a "declassify" construct—programmers can use this construct to declare intentional leakage. For instance, cryptographic signatures and ciphertexts, which are computed from private keys, are viewed as secret by information-flow analyses. Cryptographic libraries can use declassify to make this data public, as it is no longer sensitive.

In this paper, we study the impact of speculative execution in practical information-flow programming languages. First, we show that speculative execution leads to unintended leakage that violates the programmer's intent. Concretely, we present a PoC that recovers the AES key of an implementation of AES written in FaCT, a domain-specific language for constant-time programming. Our PoC is an instance of a Spectre-PHT attack; interestingly, it remains effective even if the program is compiled with Speculative Load Hardening (SLH), a compiler-based countermeasure against Spectre-PHT. Second, we propose compilerbased countermeasures for protecting programs against leakage, and show that these countermeasures achieve relative noninterference: Informally, speculative leakage of the transformed programs must correspond to sequential leakage of the original programs. One of our countermeasures is a new transformation of independent interest called selective speculative load hardening (selSLH). SelSLH optimizes SLH as implemented by the LLVM compiler, reducing the number of inserted mitigations. Third, we implement one of our countermeasures in the FaCT compiler and evaluate performance overhead for core cryptographic routines from several open-source projects. The results indicate a moderate overhead. Although we do not implement selSLH, we carry a preliminary evaluation which suggests a significant gain over SLH for cryptographic implementations.

# I. INTRODUCTION

Cryptographic software can be vulnerable to devastating side-channel attacks, allowing malicious parties to recover cryptographic keys from observing the timing behavior of programs. A common means to limit such attacks is to follow the cryptographic constant-time policy, which states that programs do not leak confidential data through an ideal model of cache-based timing side-channels. However, writing efficient constant-time cryptographic software is notoriously hard [28]. The challenges of writing constant-time cryptographic software are partially alleviated by dedicated verification or mitigation

```

public uint8 otp_and_decode(

secret uint8 m,

secret uint8 otp) {

secret mut uint8 c = m;

for (uint8 i from 0 to 8) {

c ^= (otp & (1 << i));

}

public uint8 d = declassify(c);

return decode[d];

}</pre>

```

Listing 1: One-time pad into table-based decoder. Skipping the for loop (due to misspeculation) directly leaks the secret m.

frameworks. One example of such a framework is FaCT [15], a security enhancing compiler that transforms typable programs into constant-time programs. The FaCT compiler features a constrained information-flow type system with formal guarantees. However, these guarantees have a limited scope: First, they only hold for programs without declassification. Cryptographic software, however, typically must release information (in a controlled way). Second, they only consider a sequential model of execution. Unfortunately, modern platforms often perform aggressive optimizations—one such microarchitectural optimization is speculative execution, which is at the root of the recent and devastating Spectre attacks [30]. It is possible to extend the guarantees of the FaCT compiler to programs with declassification using results from computational information flow [5, 22, 32, 33]—see also [44] for a survey on declassification. However, we are not aware of any work that studies the interactions between declassification and speculative execution.

The interaction between declassification and speculative execution can cause unintentional leaks: This is demonstrated by the FaCT program in Listing 1. In this program, a secret message m is encrypted by repeatedly performing a bitwise one-time pad; the resulting ciphertext c is fed into a table-based

decoder. Since the ciphertext depends on the secret message, it too is typed secret. For the FaCT compiler to accept this program, c must be declassified before it is fed to the decoder, as array indices can leak to an attacker (e.g., via the cache). Assuming one-time pads are uniformly distributed, it is easy to see that the program does not leak: Indeed, the ciphertext is uniformly distributed and independent from secrets, and thus the leakage is also independent of secrets.

On the other hand, if the program in Listing 1 were to somehow bypass the loop, it would trivially leak m via c. Such a scenario is clearly impossible during sequential execution; however, under adversarial speculative execution, an attacker with control over branch predictions can cause the loop condition to mispredict, skipping the loop body entirely.

Existing defenses against speculative attacks include *speculative load hardening* (SLH) [14]: Informally, SLH protects programs by masking the values of speculatively executed loads, ensuring memory safety during speculative execution. Unfortunately, applying SLH to Listing 1 does not offer any protection, as the attack does not depend on any unsafe loads from misspeculated addresses.

To analyze these undesirable interactions between declassification and speculative execution, we first develop a formal threat model (§III) and derive a simple language, semantics, and type system to express these attacks and our defenses (§IV). We then propose a new security property called relative noninterference (RNI) and an "ideal" speculative semantics for which well-typed programs are RNI (§V). To realize this idealized semantics, we develop two program transformations: Selective speculative load hardening (selSLH), an optimization over SLH which only masks values speculatively loaded into publicly-typed variables; and masked declassification, which masks values declassified during speculation. These countermeasures simulate the idealized semantics during adversarially controlled speculative execution of a program—well-typed programs transformed with these countermeasures thus satisfy RNI. We also briefly consider other countermeasures which combine (selective) SLH and add speculation fences before declassification.

We evaluate the simplest form of our countermeasure—SLH with fenced declassify—by modifying the FaCT compiler (§VI). We find that the overhead of our countermeasure on the FaCT cryptographic benchmarks is under 10%. In addition, we heuristically evaluate the performance savings of selSLH over SLH by comparing the number of public- and secret-typed loads in different cryptographic routines. Our results show that selSLH can reduce the number of masked loads in these programs by 80% or more.

Finally, we demonstrate the practical importance of RNI and our theoretical model (§VII): We develop a proof-of-concept (PoC) attack against a FaCT implementation of AES. Even when this implementation is compiled with SLH, our PoC can recover the cryptographic keys. We further demonstrate PoC attacks against two implementations of AES from OpenSSL.

We will place all software associated with this paper—the PoC attack against AES code, the FaCT benchmarks, and the heuristic analysis of selSLH—into the public domain and make it available online.

#### II. BACKGROUND

#### A. Microarchitectural channels

Modern processor microarchitectures aim to improve the performance of software, usually by predicting the future behavior of programs. For example, data caches in the processor store data that a program has recently accessed, allowing them to exploit temporal and spatial locality in software. Similarly, a processor's branch predictors monitor conditional jumps that the software executes, aiming to predict whether or not future jumps will be taken and what the destination address will be. Although the state of the microarchitecture does not affect the computation results, it does affect the program performance. Consequently, a program that monitors its own performance, e.g., by measuring the time it takes to perform certain operations, can deduce the state of the microarchitecture. Moreover, because the state of the microarchitecture is determined by program execution, monitoring the microarchitecture will leak information about past execution. Microarchitectural side-channel attacks [23] exploit these information leaks: An attacker program monitors its own performance to determine the behavior of a victim, with which it shares the use of microarchitectural components.

Microarchitectural attacks have exploited a variety of microarchitectural components, including data caches [34, 36, 51, 53], branch predictors [1, 21], translation lookaside buffers [25], and return address stacks [18]. These attacks have devastating consequences for the security of software, breaking cryptography [1, 36, 53], performing keystroke monitoring [26], reversing machine-learning models [52], reconstructing databases [45], and fingerprinting websites [46, 47].

Of particular relevance to cryptographic code are cache attacks, such as FLUSH+RELOAD [53], which can determine which memory addresses a victim program has accessed: First, the attacker evicts a monitored memory location from the cache using a dedicated instruction, such as CLFLUSH on x86 processors. The attacker then allows the victim program to execute. Finally, the attacker measures the time to access the previously evicted memory location. If the victim accessed the monitored location, that location would be cached, and the access time will be short. Otherwise, the contents of the memory location will have to come from the RAM, and the access time will be long.

# B. Spectre attacks

Modern processors use *speculative execution* as a means to improve performance. Under speculative execution, the processor fetches and executes instructions before knowing if these computations are required, rather than waiting for the results of preceding computations. A simple case of speculative execution is for branching statements: Instead of waiting for result of a branch condition, the processor may use a *branch predictor* to guess which path will be taken and start executing the predicted branch. Later, it will check whether the branch

predictor was correct, *rolling back* execution if this was not the case. The rollback mechanism ensures that architectural effects remain correct, e.g., registers and other architectural state are reset to the initial point of misspeculation. However, the microarchitectural state, such as the cache, is not rolled back. As a consequence, speculative execution can leak data that would be protected under sequential (non-speculative) execution. Attacks that exploit these predictors are known as *Spectre attacks* [30].

Listing 2: A FaCT program vulnerable to the basic Spectre-PHT attack. The function checks that the index refers to an item within the array before it accesses the array with the index, leaking the result.

Listing 2 shows a program snippet that is vulnerable against a basic Spectre attack. Because this style of attack targets the processor's pattern history table—which is responsible for branch predictions—it is termed a Spectre-PHT attack [13]. The snippet in Listing 2 ensures that all memory accesses are within the bounds of the input array. Under a sequential execution model, this snippet succeeds at its goal: If an out-of-bounds index is provided, the condition on line 3 will be false and the access will not be executed. Under a speculative execution model, however, it is possible for the body of the branch to be executed before the branch condition—even if the condition is ultimately revealed to be false. As these values are obtained from incorrect speculation, execution that depends on them will ultimately be squashed via an execution rollback. However, an attacker can encode these values into the microarchitecture state before the rollback, such as into the cache of the processor. They can then use a cache side-channel such as FLUSH+ RELOAD [53] to read the cache state and recover the value later. We refer the reader to the literature for a more extensive account of Spectre attacks [13].

#### III. THREAT MODEL

We distinguish between the *theoretical* threat model, which we use to prove the correctness of our countermeasure, and the *practical* threat model, which instantiates our theoretical threat model and which we use for our case study.

Our theoretical analysis is inspired by standard models for reasoning about side-channel leakage: We assume a victim program whose execution leaks via memory accesses and control flow, and a co-located attacker whose goal is to coerce the victim program into leaking sensitive data. The attacker can use the public interface of the victim but cannot otherwise execute code in the victim context and cannot directly read or write the victim's memory or registers. More specifically,

we assume that the attacker can influence and observe the microarchitectural state of the victim program. Following the standard Spectre-PHT threat model [16, 27], we allow the attacker full control over the prediction of conditional branches and assume the attacker can observe both the control-flow and memory trace of the program.

Our model makes two additional conservative assumptions regarding unsafe accesses and declassified values: First, we assume that target addresses of out-of-bounds memory accesses are controlled by the attacker. This allows us to abstract over the memory layout of data in the victim program. Second, we assume that the attacker immediately observes declassified values. These conservative assumptions lead to a stronger notion of security that is not tied to specific architectural models.

Our case study is carried out in an instantiation of this attack model, inspired by Patrignani and Guarnieri [37]. In this instantiation, the victim is a library code that has access to a secret heap, and the attacker is code that invokes the victim (and can also be called by the victim). However, the attacker code cannot directly access the secret data, even during misspeculated execution. This limitation can be enforced, e.g., through instrumentation [35, 49] or hardware mechanisms [29, 48, 50]. For our case study, we do not use such enforcing mechanisms; instead, our attacker simply does not access the secret data.

#### IV. SEMANTICS AND TYPING

For the theoretical analysis, we analyze programs in terms of a core imperative while-language.

#### A. Language syntax

We present the formal syntax of our language in Figure 1. Our language is a while-language with speculation fences and explicit declassification. For simplicity, we assume that memory can only be accessed through fixed-size arrays. Our language also features (constant-time) conditional expressions, which we use for our countermeasures (see Section V-C).

We let  $v \in \mathcal{V}$  range over values,  $x \in \mathcal{X}$  range over registers, and  $a \in \mathcal{A}$  range over arrays. We assume all values are either integers or booleans and we let |a| denote the size of array a. The state of a program during execution is then given by the tuple  $\langle c, \rho, \mu, b \rangle$ : The program,  $c \in \mathsf{Com}$ , is the next command (or sequence of commands) to execute. The register map,  $\rho: \mathcal{X} \to \mathcal{V}$ , maps register names to values; we write  $[e]_{\rho}$  for evaluating expression e with the register mapping  $\rho$ , and we write  $\rho[x := v]$  to update register x with value v. The memory,  $\mu: \mathcal{A} \times \mathcal{V} \to \mathcal{V}$ , maps addresses—pairs of array names and indices—to values; we write  $\mu[(a,i)]$  to retrieve the value at index i in array a; and we write  $\mu[(a,i) := v]$  to update the array a at index i with value v. Finally, the speculation flag, b, is a Boolean value; we set b to  $\top$  when the program is misspeculating.

# B. Speculative semantics

Formally, we model speculative execution as an instrumented adversarial semantics inspired by [9, 16]. This style of

```

e \in \mathsf{Expr} ::= v

value

register

op(e, \ldots, e)

operator

conditional expression

c \in \mathsf{Com} ::= \mathsf{skip}

empty, do nothing

c; c

sequence

assignment

x := e

x :=_{\mathsf{declassify}} e

declassification

load from array a offset e

x := a|e|

a[e] := e

store to array a offset e

if t then c else c

conditional

while t do c

while loop

fence

fence

```

Figure 1: Syntax of programs.

semantics departs from classic semantics by using explicit *observations* to model side-channel leakage and *adversarial directives* for modeling adversarial control over branch prediction and out-of-bounds accesses.

One-step execution of programs is given by a labeled transition relation between states:

$$\langle c, \rho, \mu, b \rangle \xrightarrow{o} \langle c', \rho', \mu', b' \rangle$$

The directive d and observation o are taken from the following syntaxes:

```

\begin{array}{ll} d \in \mathsf{Dir} & ::= & \mathsf{step} \mid \mathsf{force} \mid \mathsf{load} \ a, i \mid \mathsf{store} \ a, i \\ o \in \mathsf{Obs} & ::= & \bullet \mid \mathsf{read} \ a, v \mid \mathsf{write} \ a, v \mid \mathsf{branch} \ b \mid \mathsf{decl} \ v \end{array}

```

Each observation o represents a potential leak of information in the standard constant-time model [8]. The read a, v and write a, v observations, respectively, capture information that is leaked via the cache or other memory side-channel attacks [47, 53]. Similarly, the branch b observation captures information an attacker can recover from the control flow of the program, such as through port contention [2] or instruction cache analysis [1, 21]. In addition, we include an observation decl v that immediately leaks any values that are explicitly declassified, as we conservatively assume that the attacker will observe any declassified information.

The adversarial directives d allow our modeled attacker to control the speculative behavior of a program during execution. For example, to represent an attacker that can cause a conditional branch to take an misspeculated path, we allow the attacker to supply the directive force, which forces the program down the wrong branch. Similarly, when a program is about to perform an unsafe load or store, we conservatively allow the attacker to control the address that is read from (or written to) with the directive load a,i (resp. store a,i). Otherwise, the attacker can supply the directive step, which simply executes the program as per the usual semantics.

We provide our execution rules in Figure 2. Our rules are similar to usual semantics for a simple while-language: Rules [SEQ-SKIP] and [SEQ] allow empty commands and command sequencing, while rule [ASSIGN] evaluates a given expression e using the register file  $\rho$  and updates the register x accordingly. We describe in detail our divergence from usual semantics:

Conditional branching. Conditional branches (rule [IF]) evaluate their branch expression t, continuing down the associated branch. The value of the condition is leaked to the attacker via the observation branch  $[t]_{\rho}$ . While loops (rule [WH]) proceed similarly, leaking the loop condition on each iteration. We also allow the attacker to force conditional branches and while loops to misspeculate the result of their respective conditions (rules [IF-S] and [WH-S]). When the attacker issues the directive force instead of step, these rules cause execution to proceed down the *incorrect* branch. Accordingly, we update the speculation flag b to  $\top$  to signal that we have misspeculated. Because the force directive always forces the incorrect path, we know that  $b = \top$  if and only if we have diverged from sequential execution.

**Memory operations.** All memory operations in our semantics are given as indices into discrete arrays. For *safe* accesses (rules [LD] and [ST]) where the evaluated index  $[e]_{\rho}$  is inbounds for a, we leak the memory address via observation read a,  $[e]_{\rho}$  (resp. write a,  $[e]_{\rho}$ ). We assume all programs are memory-safe during sequential execution. However, during misspeculation, an attacker may coerce a program to perform *unsafe* memory operations (rules [LD-U] and [ST-U]). If, during a misspeculated memory operation, the index e is out-of-bounds for array a (that is,  $[e]_{\rho} \notin [0, |a|)$ ), then we conservatively allow the attacker to explicitly specify the memory address that actually gets accessed. In this case, the attacker issues the directive load a', i (resp. store a', i) that determines the address that is loaded from (or stored to) in memory—this may use a different array entirely.

**Speculation barriers.** Modern processors include *speculation barrier* instructions that halt execution and wait for all speculation to properly resolve. We model speculation barriers in our language with the fence command (rule [FEN]), which only allows execution to continue if the current execution has never misspeculated (that is,  $b = \bot$ ). Otherwise, if we have misspeculated (i.e.,  $b = \top$ ) then we let execution get stuck.

**Declassification.** Declassified assignment (rule [DECL]) is semantically similar to regular assignment. However, we explicitly leak the value of the expression e to the attacker via the observation decl  $[e]_{\varrho}$ .

The following lemma summarizes key structural properties of execution:

Lemma 1. If

$$\langle c, \rho, \mu, b \rangle \xrightarrow{o} \langle c', \rho', \mu', b' \rangle$$

then:

- If  $b = \top$  then  $b' = \top$ .

- If  $b = \bot$  and  $b' = \top$  then d = force.

- If  $d = \text{load } a, v, \text{store } a, v \text{ then } b = \top$ .

<sup>&</sup>lt;sup>1</sup>For simplicity, we assume programs do not contain instructions with data-depending timing.

The first item states that there is no way for b to reset to  $\bot$  once it has been set; we purposefully do not model speculative rollback, as it is unnecessary when considering all possible execution paths as in our analysis [9]. The second item states that the only way for b to become  $\top$  (i.e., for execution to misspeculate) is through the force directive. Thus every execution of a program follows sequential semantics up until the point of misspeculation (if any occurs). The last item states that unsafe accesses only happen during speculative execution.

**Complete executions.** We let  $\langle c, \rho, \mu, b \rangle \xrightarrow[D]{\mathcal{O}} \langle c', \rho', \mu', b' \rangle$  denote the labeled reflexive-transitive closure of single-step execution. Moreover, we write  $\langle c, \rho, \mu, \bot \rangle \Downarrow_D^{\mathcal{O}}$  when  $\langle c, \rho, \mu, \bot \rangle \xrightarrow[D]{\mathcal{O}} \langle \text{skip}, \rho', \mu', b' \rangle$  or  $\langle c, \rho, \mu, \bot \rangle \xrightarrow[D]{\mathcal{O}} \langle \text{fence}, \rho', \mu', \top \rangle$ : The first case corresponds to a complete execution that has terminated and the second to a misspeculated execution that has become stuck. When execution remains entirely sequential, i.e., all directives are step, we write  $\langle c, \rho, \mu \rangle \Downarrow_D^{\mathcal{O}}$  instead of  $\langle c, \rho, \mu, \bot \rangle \Downarrow_D^{\mathcal{O}}$ .

# C. Typing environment and speculation

We assume that every register and array is tagged with a security level. For simplicity, we only consider the lattice of security levels  $L \leqslant H$ , where H is secret data and L is public data: Public values can be treated as secret, but not vice versa (unless explicitly declassified). Other choices of security lattices are possible, but are not considered in this paper. Additionally, we do not consider arrays with mixed sensitivity—arrays are either entirely public or entirely secret.

We use  $\Gamma$  to denote the static typing environment;  $\Gamma(x)$  and  $\Gamma(a)$  represent the security levels of registers x and arrays a respectively. We extend  $\Gamma$  to arbitrary expressions by setting  $\Gamma(e) = \max_{x \in \mathsf{Vars}(e)} \Gamma(x)$ , where  $\mathsf{Vars}(e)$  is the set of variables contained in e.

We present our typing rules in Figure 3. As usual, we allow public values to be assigned to secret variables, but not vice-versa: Rule [ASSIGN] specifies  $\Gamma(e) \leqslant \Gamma(x)$  for x:=e to be well-typed. Rules [LD] and [ST] enforce similar constraints. In addition, memory and control-flow commands use constant-time typing rules [15, 16]: Array indices must be public ( $\Gamma(e)=L$  in rules [LD] and [ST]), since memory addresses are leaked to the attacker during execution. Similarly, control flow can only depend on public branching conditions ( $\Gamma(t)=L$  in rules [IF] and [WH]) since the branch conditions are also leaked. Finally, explicit declassification (rule [DECL]) allows secret values to be assigned to public variables with no constraints on the type of e.

With this type system, well-typed programs without declassification will be secure under standard execution, since only public values can leak via observations. We formalize this claim using the standard notion of low-equivalence:

**Definition 1** (Low equivalence).  $(\rho_1, \mu_1) \sim (\rho_2, \mu_2)$  iff  $\rho_1(x) = \rho_2(x)$  for every  $x \in \mathcal{X}$  such that  $\Gamma(x) = L$  and  $\mu_1(a) = \mu_2(a)$  for every  $a \in \mathcal{A}$  such that  $\Gamma(a) = L$ .

$$\begin{array}{c} \rho' = \rho[x := \llbracket e \rrbracket_{\rho}] \\ \hline \langle x := e, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle \text{skip}, \rho', \mu, b \rangle} \text{ [ASSIGN]} \\ \hline (x := e, \rho, \mu, b) \xrightarrow[\text{step}]{\bullet} \langle \text{skip}, \rho', \mu, b \rangle} \text{ [LD]} \\ \hline \langle x := a[e], \rho, \mu, b \rangle \xrightarrow[\text{read } a, \llbracket e \rrbracket_{\rho}]{\bullet} \langle \text{skip}, \rho', \mu, b \rangle} \text{ [LD]} \\ \hline \langle x := a[e], \rho, \mu, \top \rangle \xrightarrow[\text{load } a', i]{\bullet} \langle \text{skip}, \rho', \mu, \top \rangle} \text{ [LD-U]} \\ \hline \langle x := a[e], \rho, \mu, \top \rangle \xrightarrow[\text{load } a', i]{\bullet} \langle \text{skip}, \rho', \mu, \top \rangle} \text{ [ST]} \\ \hline \begin{bmatrix} e \rrbracket_{\rho} \in [0, |a|) & \mu' = \mu[(a, \llbracket e \rrbracket_{\rho}) := \llbracket e' \rrbracket_{\rho}] \\ \langle a[e] := e', \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle \text{skip}, \rho, \mu', b \rangle} \text{ [ST]} \\ \hline \begin{bmatrix} e \rrbracket_{\rho} \notin [0, |a|) & i \in [0, |a'|) & \mu' = \mu[(a', i) := \llbracket e' \rrbracket_{\rho}] \\ \langle a[e] := e', \rho, \mu, \top \rangle \xrightarrow[\text{store } a', i]{\bullet} \langle \text{skip}, \rho, \mu', \top \rangle \\ \hline \langle a[e] := e', \rho, \mu, b \rangle \xrightarrow[d]{\bullet} \langle c'_1, \rho', \mu', b' \rangle \\ \hline \langle a[e] := e', \rho, \mu, b \rangle \xrightarrow[d]{\bullet} \langle c'_1, \rho', \mu', b' \rangle \\ \hline \langle c_1, \rho, \mu, b \rangle \xrightarrow[d]{\bullet} \langle \text{skip}, \rho', \mu', b' \rangle \\ \hline \langle c_1, \rho, \mu, b \rangle \xrightarrow[d]{\bullet} \langle \text{skip}, \rho', \mu', b' \rangle \\ \hline \langle c_1, c_2, \rho, \mu, b \rangle \xrightarrow[d]{\bullet} \langle c'_1, c_2, \rho', \mu', b' \rangle \\ \hline \langle \text{if } t \text{ then } c_{\top} \text{ else } c_{\bot}, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle c_{\llbracket t \rrbracket_{\rho}}, \rho, \mu, b \rangle \\ \hline \langle \text{if } t \text{ then } c_{\top} \text{ else } c_{\bot}, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle c_{\llbracket t \rrbracket_{\rho}}, \rho, \mu, b \rangle \\ \hline \langle \text{while } t \text{ do } c, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle c_{\llbracket t \rrbracket_{\rho}}, \rho, \mu, b \rangle \\ \hline \langle \text{while } t \text{ do } c, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle c_{\llbracket t \rrbracket_{\rho}}, \rho, \mu, \tau \rangle \\ \hline \langle \text{while } t \text{ do } c, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle \text{skip}, \rho, \mu, \bot \rangle \\ \hline \langle \text{while } t \text{ do } c, \rho, \mu, b \rangle \xrightarrow[\text{step}]{\bullet} \langle \text{skip}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step} \langle \text{chil}_{\rho}, \rho, \mu, \bot \rangle \\ \hline \langle \text{step}$$

Figure 2: One-step (adversarial) semantics.

**Lemma 2.** If  $\vdash c$  is declassify-free and  $(\rho_1, \mu_1) \sim (\rho_2, \mu_2)$  and  $\langle c, \rho_1, \mu_1 \rangle \Downarrow^{\mathcal{O}_1}$  and  $\langle c, \rho_2, \mu_2 \rangle \Downarrow^{\mathcal{O}_2}$  then  $\mathcal{O}_1 = \mathcal{O}_2$ .

Lemma 2 states that if two executions have low-equivalent initial states—i.e., that they agree on all public values—then they will have identical sequential observation traces. An attacker thus cannot recover any secret information. However, under *speculative* execution, this no longer holds: even if a program is well-typed, an attacker can force the program down

$$\begin{split} & \frac{\Gamma(e) \leqslant \Gamma(x)}{\Gamma \vdash x := e} \text{ [ASSIGN]} \\ & \frac{\Gamma(e) \leqslant \Gamma(x)}{\Gamma \vdash x := e} \text{ [LD]} \\ & \frac{\Gamma(e) = L \qquad \Gamma(a) \leqslant \Gamma(x)}{\Gamma \vdash x := a[e]} \text{ [LD]} \\ & \frac{\Gamma(e) = L \qquad \Gamma(e') \leqslant \Gamma(a)}{\Gamma \vdash a[e] := e'} \text{ [ST]} \\ & \frac{\Gamma(t) = L \qquad \Gamma \vdash c_1 \qquad \Gamma \vdash c_2}{\Gamma \vdash \text{ if } t \text{ then } c_1 \text{ else } c_2} \text{ [IF]} \\ & \frac{\Gamma(t) = L \qquad \Gamma \vdash c}{\Gamma \vdash \text{ while } t \text{ do } c} \text{ [WH]} \\ & \frac{\Gamma \vdash c_1 \qquad \Gamma \vdash c_2}{\Gamma \vdash c_1; c_2} \text{ [SEQ]} \\ & \frac{\Gamma(x) = L}{\Gamma \vdash x :=_{\text{declassify } e}} \text{ [DECL]} \end{split}$$

Figure 3: Standard constant-time typing with declassification.

misspeculated paths to reveal secret information.

We present one such example, the classic Spectre-PHT attack, in Listing 2. Sequentially, this program can only access (and leak) the public values from array. However, if the attacker controls the value of index to be out-of-bounds, but forces the branch on line 3 to misspeculate, they can retrieve any arbitrary value from memory—including secret values from elsewhere in the program.

A more subtle problem is that attackers can cause *unintended declassification*, as seen in Listing 1. Sequentially, the masking result c is declassified only after being properly masked. Even though this result is leaked via the access to table, the attacker normally only learns the final obfuscated value. However, if the attacker forces the loop condition to misspeculate (and thus skip the loop body entirely), the result c that gets declassified and leaked is exactly the original secret input m.

#### V. RELATIVE NON-INTERFERENCE

Broadly speaking, it is a standard practice to model security policies as information-flow policies. These policies can be *direct* or *relative—direct* policies require that related executions yield equal leakage, whereas *relative* policies instead require that related executions in one setting do not leak *more* than related executions in another setting [17]. Direct policies offer stronger guarantees than relative policies, but cannot always be achieved.

In the classic sequential setting, most security policies enforce *non-interference*; informally, non-interference states that an attacker cannot distinguish between two executions of the same program that use the same public inputs but possibly different secret inputs. However, simple non-interference does

not hold for programs that use declassification. Notions such as *robust declassification* [54] extend non-interference to handle these cases: Intuitively, robust declassification states that *passive* attackers do not learn more than *active* attackers. Robust declassification is an instance of a relative policy, i.e., it compares leakage in two execution scenarios.

Because our language includes declassification, we frame our own security policy as a relative property—concretely, we evaluate the speculative security of a program relative to its sequential behavior: During speculative execution, a program should not reveal more information to an attacker than it would have sequentially. We formalize this property as *relative non-interference* (RNI).

# A. Relative non-interference

We define relative non-interference (RNI) as a relative policy which contrasts the speculative and sequential leakage observations of a program. Our notion is inspired by prior speculative non-interference properties [17, 27] and is a form of *robust declassification* [54] in the speculative domain.

**Definition 2.** A program c is RNI iff for every pair of executions  $\langle c, \rho_1, \mu_1, \bot \rangle \Downarrow_D^{\mathcal{O}_1}$  and  $\langle c, \rho_2, \mu_2, \bot \rangle \Downarrow_D^{\mathcal{O}_2}$  such that  $(\rho_1, \mu_1) \sim (\rho_2, \mu_2)$  we have:

$$\mathcal{O}_1^* = \mathcal{O}_2^* \Longrightarrow \mathcal{O}_1 = \mathcal{O}_2$$

where  $\langle c, \rho_1, \mu_1, \bot \rangle \downarrow_{D^*}^{\mathcal{O}_1^*}$  (resp.  $\mathcal{O}_2^*$ ) and  $D^*$  is the longest prefix of D that does not contain the directive force.

Formally, RNI requires that for every set of directives D and every two executions of c from equivalent states, equality of leakage until the first force directive—the directive that triggers misspeculation—entails equality of leakage for the complete execution.

As we see in Listings 1 and 2, well-typed programs can still fail to satisfy RNI. However, given a well-typed program c, we can transform it into a *sequentially equivalent* program c' that does satisfy RNI: Under sequential execution, c' will produce the same output and the same sequence of observations as c. We formalize the transformation in two steps: We first define an idealized semantics and show that well-typed programs satisfy RNI under this idealized semantics. Then, we show that the idealized semantics can be implemented by a program transformation.

# B. Idealized semantics

The idealized semantics protects instructions that would speculatively leak secrets—namely, declassify and load instructions. We find, however, that loads that already operate on secret arrays (i.e.,  $\Gamma(a)=H$ ) do not need to be protected: Even under adversarial misspeculation, they will continue to load secret values into secret registers. Therefore, the idealized semantics only differs from the original semantics in the following two ways:

Public loads: The target register is updated with a default value when the speculation flag is set to true. • Declassify: The target register is updated with a default value when the speculation flag is set to true.

$$\frac{\llbracket e \rrbracket_{\rho} \in [0,|a|) \qquad \rho' = \rho[x := \mu[(a,\llbracket e \rrbracket_{\rho})]]}{\langle x := a[e], \rho, \mu, \bot \rangle} \text{ [LD]}$$

$$\frac{\Gamma(a) = H}{\langle x := a[e], \rho, \mu, \top \rangle} \frac{\llbracket e \rrbracket_{\rho} \notin [0,|a|)}{\text{step}} \langle \text{skip}, \rho', \mu, \bot \rangle$$

$$\frac{i \in [0,|a'|) \qquad \rho' = \rho[x := \mu[(a',i)]]}{\langle x := a[e], \rho, \mu, \top \rangle} \frac{\text{read } a, \llbracket e \rrbracket_{\rho}}{\text{load } a',i} \langle \text{skip}, \rho', \mu, \top \rangle} \text{ [LD-U]}$$

$$\frac{\Gamma(a) = L \qquad \rho' = \rho[x := 0]}{\langle x := a[e], \rho, \mu, \top \rangle} \frac{\text{read } a, \llbracket e \rrbracket_{\rho}}{\text{step}} \langle \text{skip}, \rho', \mu, \top \rangle} \text{ [DECL]}$$

$$\frac{\rho' = \rho[x := \llbracket e \rrbracket_{\rho}]}{\langle x :=_{\text{declassify}} e, \rho, \mu, \bot \rangle} \frac{\rho' = \rho[x := 0]}{\text{step}} \langle \text{skip}, \rho', \mu, \bot \rangle} \text{ [DECL-PROT]}$$

$$\frac{\rho' = \rho[x := 0]}{\langle x :=_{\text{declassify}} e, \rho, \mu, \top \rangle} \frac{\rho' = \rho[x := 0]}{\text{step}} \langle \text{skip}, \rho', \mu, \top \rangle} \text{ [DECL-PROT]}$$

Figure 4: Selected rules for idealized semantics.

We formalize the idealized semantics in Figure 4 with a new step relation  $\langle c, \rho, \mu, b \rangle \xrightarrow[d]{o} \langle c', \rho', \mu', b' \rangle$  and we write complete executions of the idealized semantics as  $\langle c, \rho, \mu, b \rangle \parallel_D^{\mathcal{O}} \langle c', \rho', \mu', b' \rangle$ . As before, we omit b and D when considering a sequential execution of the program.

We now show the equivalence of the original and idealized semantics:

**Lemma 3** (Equivalence of sequential semantics). Well-typed programs have equivalent leakage and functional behavior under both semantics:

$$\langle c, \rho, \mu \rangle \Downarrow^{\mathcal{O}} \langle c', \rho', \mu' \rangle \text{ iff } \langle c, \rho, \mu \rangle \Downarrow^{\mathcal{O}} \langle c', \rho', \mu' \rangle.$$

The proof of the lemma is by inspection of the semantic rules for single-step execution followed by induction on the length of the complete execution.

Next, we show that well-typed programs are RNI under idealized semantics:

**Proposition 1** (RNI with idealized semantics). *If*  $\vdash$  *c then c is RNI when executed with the idealized semantics.*

The lemma is derived from two unwinding lemmas [41]. The unwinding lemma for sequential execution considers two single-step executions with the same directive and observation and shows preservation of equivalence for register maps and memories.

**Lemma 4** (Unwinding lemma for sequential execution). *Let* d = step, force. *If*  $\vdash c$ , *then for every pair of execution steps:*

$$\langle c, \rho_1, \mu_1, \perp \rangle \xrightarrow{o_1} \langle c'_1, \rho'_1, \mu'_1, b'_1 \rangle$$

$$\langle c, \rho_2, \mu_2, \perp \rangle \xrightarrow{o_2} \langle c'_2, \rho'_2, \mu'_2, b'_2 \rangle$$

we have:

$$(\rho_1, \mu_1) \sim (\rho_2, \mu_2) \wedge o_1 = o_2$$

$$\Longrightarrow (\rho'_1, \mu'_1) \sim (\rho'_2, \mu'_2) \wedge c'_1 = c'_2 \wedge b'_1 = b'_2.$$

Proof. See Appendix A.

The unwinding lemma for speculative execution considers two executions with the same directive and shows preservation of equivalence for register maps and observations.

**Lemma 5** (Unwinding lemma for idealized speculative execution). *If*  $\vdash$  *c then for every pair of execution steps:*

$$\langle c, \rho_1, \mu_1, \top \rangle \xrightarrow{o_1} \langle c'_1, \rho'_1, \mu'_1, \top \rangle$$

$$\langle c, \rho_2, \mu_2, \top \rangle \xrightarrow{o_2} \langle c'_2, \rho'_2, \mu'_2, \top \rangle$$

we have:

$$\rho_1 \sim \rho_2 \implies o_1 = o_2 \wedge \rho_1' \sim \rho_2' \wedge c_1' = c_2'$$

Proof. See Appendix A.

*Proof of Proposition 1.* W.l.o.g.  $D = \text{step}^n :: \text{force} :: D'$  and we can decompose the two executions as:

$$\langle c, \rho_1, \mu_1, \top \rangle \xrightarrow{O_1:o_1} \langle c_1', \rho_1', \mu_1', \bot \rangle \xrightarrow{O_1'} \langle \mathsf{fence}, \rho_1', \mu_1', \bot \rangle$$

$$\langle c, \rho_2, \mu_2, \top \rangle \xrightarrow{O_2:o_2} \langle c_2', \rho_2', \mu_2', \top \rangle \xrightarrow{O_2'} \langle \mathsf{fence}, \rho_2', \mu_2', \bot \rangle$$

where  $D' = \operatorname{step}^n ::$  force and D = D' :: D''. Assume that  $O_1 = O_2$ . By repeated applications of Lemma 4, it follows that the instructions and the memories *before* executing the force step are equivalent. Since force executes on a public branching instruction, the two force steps leak the same observations, i.e.,  $o_1 = o_2$  and hence by one final application of Lemma 4 we conclude that  $c_1' = c_2'$  and that  $(\rho_1', \mu_1') \sim (\rho_2', \mu_2')$ . By repeated applications of Lemma 5, we conclude that  $O_1' = O_2'$ , and hence  $O_1 :: o_1 :: O_1' = O_2 :: o_2 :: O_2'$ , as desired.

# C. Program transformation

To implement the idealized semantics, we define a concrete program transformation (c). We present the transformation rules in Figure 5. Our transformations make the misspeculation flag b concrete, instrumenting programs to track its value in a (unique) architectural register  $\tilde{b}$ . In particular, we update  $\tilde{b}$  when entering a branch or a loop body and after exiting a loop. We use  $\tilde{b}$  to implement the *selective SLH* and *masked declassify* countermeasures, which respectively protect memory loads and declassification statements.

SelSLH, or selective speculative load hardening, masks the results of public memory loads against  $\tilde{b}$ . Hence if  $\tilde{b}$  is  $\top$ —i.e., the program has misspeculated—then the result of the load becomes 0. However, selSLH explicitly does not transform secret loads; this is an improvement over speculative load hardening (SLH), which masks all loads. SelSLH is particularly relevant for cryptographic programs, since such programs mainly operate on secret data. Since selSLH only masks the public loads and ignores the secret loads, it drastically reduces the number of mitigations inserted to protect most

Figure 5: Selective SLH and masked declassification countermeasures. Transformation of loads is predicated on the type of x.

cryptographic programs. We present some preliminary results of the potential savings in Section VI-C.

Masked declassification simply masks the results of declassification against  $\tilde{b}$ . Just as with selSLH, if the program has misspeculated, the result of the operation becomes 0.

Finally, we prove that our transformation properly implements the idealized semantics: Given a program c, the ideal execution of c agrees with the execution of the transformed program (c). We leave the formal definition of agreement to the appendix (as Lemma 7) and state the correctness in a simplified form:

**Lemma 6** (Implementation of idealized semantics, simplified). *The following are equivalent:*

- $\langle c, \rho, \mu, b \rangle \Downarrow_D^{\mathcal{O}} \langle c', \rho', \mu', b' \rangle$

- $\bullet \ \left< \langle \! \langle \! \langle c \rangle \! \rangle, \rho [\tilde{b} \! := \! b], \mu, b \right> \Downarrow_D^{\mathcal{O}} \left< c', \rho' [\tilde{b} \! := \! b'], \mu', b' \right>$

The lemma is proved by induction on the length of execution. Although we focus on selSLH and masked declassification, in practice developers may be forced to fall back to alternatives. In particular, without compiler support for public/secret type information, we must conservatively mask every array access. Similarly, it is not feasible to implement masked declassification without proper compiler support. In this case, we can instead use *fenced declassification*: Instead of masking the result of declassification, we insert a fence instruction before each declassify statement—since fences prevent misspeculated execution from proceeding, unintended values cannot be declassified.

These alternative countermeasures are still sound: We can easily define an corresponding idealized semantics and transformation for each combination of countermeasures; the proofs of these countermeasures proceed in exactly the same way. However, these alternative countermeasures have a higher performance overhead, as we see in our evaluation.

#### VI. IMPLEMENTATION AND EVALUATION

We evaluate the performance of SLH and fenced declassification using FaCT [15], a domain-specific framework for writing efficient constant-time cryptographic routines. FaCT is an ideal target for implementing our countermeasure: First, the FaCT language already supports information-flow typing and declassify statements; second, the FaCT compiler is built on LLVM compiler infrastructure, which already supports SLH;

Table I: Case study summary: Lines of code in FaCT and uses of declassify (#D).

| Case study              | LoC  | #D |

|-------------------------|------|----|

| libsodium secretbox     | 1068 | 1  |

| curve25519-donna-c64    | 342  | 1  |

| OpenSSL record validate | 91   | 1  |

| OpenSSL MEE-CBC         | 219  | 1  |

and third, FaCT offers formal guarantees which blend in nicely with our approach.

# A. FaCT implementation

FaCT [15] is a framework for writing efficient constant-time code. The framework consists of two components: The FaCT language, a domain-specific language supported by an information-flow type system; and the FaCT compiler, which generates efficient constant-time code. In order to ease programming, the type system of the FaCT language is permissive towards secret-dependent control flow—instead, FaCT relies on type-directed transformations to remove potential timing leaks. These transformations yield programs typable in a type system similar to the one from Figure 3; the resulting programs are converted to LLVM IR, which is assembled by Clang.

The FaCT distribution includes ports of code from several well-known open-source cryptographic libraries, including the NaCl *secretbox* functions [11] from libsodium [20], a user-friendly high-speed cryptographic library; Curve25519 donnac64 [31], an elliptic-curve Diffie-Hellman function introduced by Bernstein [10]; OpenSSL [38] *ssl3\_cbc\_digest\_record* function which verifies the SSLv3 decrypted messages; and OpenSSL [38] *aesni\_cbc\_hmac\_sha1\_cipher* function which is called in MAC-then-Encode-then-CBC-Encrypt (MEE-CBC). These functions exercise all of the language features of FaCT, cover a broad range of algorithms, and showcase the use of FaCT in different settings, from implementing individual procedures to large portions of libraries [15]. We provide an indication of the size of each port and of number of declassify statements in Table I.

Implementing SLH and fenced declassification required two modifications to the FaCT compiler:

We modified code generation to insert a fence instruction before each declassification. Concretely, our implementa-

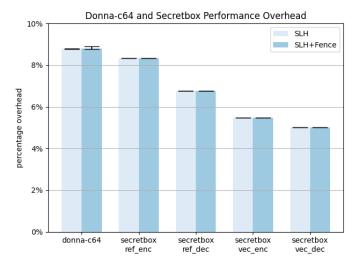

Figure 6: Overhead of SLH, SLH+Fence compared to regular FaCT in Curve25519 donna-c64 and libsodium's secretbox

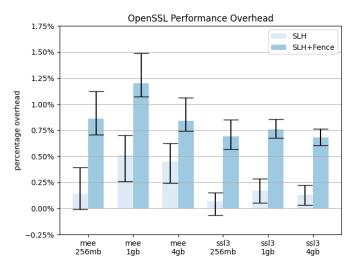

Figure 7: Overhead of SLH, SLH+Fence compared to regular FaCT in OpenSSL operations

tion inserts the *llvm.x86.sse2.lfence* LLVM intrinsic before changing the security label.

We upgraded FaCT's backend to LLVM 11 to make use of LLVM's -mspeculative-load-hardening option.

# B. Performance evaluation

Our performance evaluation uses the case studies from FaCT distribution. We apply the following changes to these examples:

- Instead of measuring the average over many executions of the same routine as in [15], we measure individual executions and report median and quartiles. This is a standard practice to eliminate outliers due to system interrupts.

- Benchmarking much faster pieces of code requires a higherresolution timer than the one used in the FaCT distribution; we use the CPU's built-in cycle counter.

We declassify the output of Curve25519 and secretbox encryption. This is not required by the FaCT type system, but it reflects that output of Curve25519 public-key generation and of authenticated encryption are public and considered safe to be leaked by the caller.

We ran benchmarks of these artifacts with unmodified FaCT, FaCT with LLVM's SLH enabled, and with FaCT with both SLH and the fenced declassify modification. We used a machine with an Intel i7-9700K CPU and 64GB RAM; this CPU does not feature hyperthreading and we disabled the TurboBoost feature for consistency. We present our results in Figures 6 and 7 and we report the absolute cycle counts in Table II. We find that the overhead introduced by SLH is significant, but the additional overhead introduced by fenced declassification is very small: In cryptographic software, declassification is required, although rare, and usually only upon the final output. The OpenSSL benchmarks in Figure 7 show a smaller overhead compared to the libsodium benchmarks in Figure 6; this is because the OpenSSL benchmarks are much less CPU-bound.

# C. Performance of selSLH

Implementing selSLH requires major changes to the LLVM compiler—including implementing a security type system for the LLVM IR—and is out of scope of this paper. However, in order to obtain a preliminary understanding of the benefits of selective SLH, we analyze implementations of two widely used cryptographic primitives: The reference implementation of ChaCha20 by Bernstein, as an example of a primitive that has a public variable input length; and the donnac64 implementation by Langley of scalar multiplication on Curve25519, as an example of a primitive with all inputs and outputs of fixed length. We compiled both implementations with gcc-10.2 and optimization flags -fomit-frame-pointer—march=native on a machine with an Intel i7-6500U CPU.

For our evaluation, we modify the Pitchfork analysis tool [16], which uses symbolic execution to verify binaries for sequential (and speculative) constant-time. More importantly for us, Pitchfork propagates the security types of values through execution when given the initial types of inputs and global data. We instrument Pitchfork to classify and count each load it encounters during sequential execution.

With selSLH, the security type of inputs has a direct impact on performance—secret inputs will not have mitigations applied. Thus, for our evaluation, we declare all inputs to be secret unless they *must* be public to be well-typed (i.e., values are sequentially leaked). For example, while the fixed basepoint of Curve25519 in the donna-c64 implementation is public in principle, declaring it as secret is not unsound, and results in fewer public loads (and thus gives better performance with selSLH).

We present our results in Table III—our experiments show that for typical cryptographic code, we can indeed safely and soundly omit the majority of SLH protections. In the ChaCha20 implementation, for example, nearly 80% of the loads are for secret data, and thus need not be protected by SLH; the remaining loads access public pointers and loop counters spilled

| Table II: Benchmarks summary | . I ouver questile | madian and    | unnar auartila | for anoh implementation  |

|------------------------------|--------------------|---------------|----------------|--------------------------|

| Table II. Denchmarks summary | : Lower duartile   | , median, and | ubber duartne  | for each implementation. |

|                              |                    |               |                |                          |

| Implementation    | F       | aCT (plair | 1)      | Cpucycle counts: $P_{25}$ , $P_{50}$ , $P_{75}$<br>FaCT w/ SLH |         |         | FaCT w/ SLH+Fence |         |         |

|-------------------|---------|------------|---------|----------------------------------------------------------------|---------|---------|-------------------|---------|---------|

| donna             | 1.96e5  | 1.96e5     | 1.96e5  | 2.13e5                                                         | 2.13e5  | 2.13e5  | 2.13e5            | 2.13e5  | 2.13e5  |

| secretbox ref enc | 2.03e3  | 2.03e3     | 2.03e3  | 2.20e3                                                         | 2.20e3  | 2.20e3  | 2.23e3            | 2.23e3  | 2.23e3  |

| secretbox ref dec | 2.93e3  | 2.93e3     | 2.93e3  | 3.12e3                                                         | 3.12e3  | 3.12e3  | 3.14e3            | 3.14e3  | 3.15e3  |

| secretbox vec enc | 1.93e3  | 1.93e3     | 1.94e3  | 2.04e3                                                         | 2.04e3  | 2.04e3  | 2.07e3            | 2.07e3  | 2.07e3  |

| secretbox vec dec | 2.83e3  | 2.83e3     | 2.83e3  | 2.97e3                                                         | 2.97e3  | 2.97e3  | 2.98e3            | 2.98e3  | 2.98e3  |

| mee 256mb         | 2.31e9  | 2.31e9     | 2.31e9  | 2.31e9                                                         | 2.31e9  | 2.31e9  | 2.32e9            | 2.33e9  | 2.33e9  |

| mee 1gb           | 9.22e9  | 9.23e9     | 9.23e9  | 9.25e9                                                         | 9.27e9  | 9.29e9  | 9.32e9            | 9.34e9  | 9.37e9  |

| mee 4gb           | 3.68e10 | 3.69e10    | 3.69e10 | 3.70e10                                                        | 3.70e10 | 3.71e10 | 3.71e10           | 3.72e10 | 3.73e10 |

| ss13 256mb        | 3.09e9  | 3.10e9     | 3.10e9  | 3.09e9                                                         | 3.10e9  | 3.10e9  | 3.11e9            | 3.12e9  | 3.12e9  |

| ssl3 1gb          | 1.23e10 | 1.23e10    | 1.24e10 | 1.24e10                                                        | 1.24e10 | 1.24e10 | 1.24e10           | 1.24e10 | 1.25e10 |

| ssl3 4gb          | 4.95e10 | 4.95e10    | 4.96e10 | 4.95e10                                                        | 4.96e10 | 4.96e10 | 4.98e10           | 4.99e10 | 4.99e10 |

Table III: Counts of public and secret loads of various cryptographic programs. We report the percentage reduction of mitigations that selective SLH would provide as compared to traditional SLH.

| Impl.             | # public | # secret | # total | SLH saved |

|-------------------|----------|----------|---------|-----------|

| ChaCha20 (512 B)  | 192      | 766      | 958     | 79.96%    |

| ChaCha20 (1024 B) | 384      | 1,518    | 1,902   | 79.81%    |

| donna-c64         | 2,054    | 43,663   | 45,717  | 95.51%    |

to the stack (and must remain protected). For the donna-c64 implementation of Curve25519, the savings reach more than 95%—selSLH is able to remove nearly *all* SLH protections.

#### VII. CASE STUDY: AES

Section V demonstrates that interactions between declassification and speculative execution may breach the security guarantee of a program. In this section we demonstrate some of the risks that this may cause in realistic scenarios. We investigate declassification in the common case of AES encryption, where declassification is required to allow transmitting the ciphertext. We demonstrate that due to speculative execution, the ciphertext may be declassified too early leading to disclosure of an improperly encrypted message. We leave a description of how to recover a key from such messages to Appendix B.

More specifically, we look at an implementation of AES written in FaCT that uses the AES-NI instruction set to perform the encryption rounds. Successive rounds are implemented as straight-line code with two branches that exit early after ten or twelve rounds to allow for the different key lengths of AES. We further look at two implementations that are part of OpenSSL, the default implementation, which uses AES-NI, and a machine-independent version that uses T-tables. Before describing our attack, we present a short refresher on the AES encryption.

#### A. AES Background

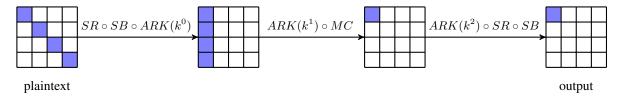

The Advanced Encryption Standard (AES) is a symmetric block-cipher, operating on 128-bit block size using keys of size 128, 192, or 256 bits. AES follows a substitution-permutation

network design whose construction consists of multiple rounds to produce a ciphertext.

**AES Round Overview.** The 128-bit AES state is written as a  $4 \times 4$  byte matrix and in each round transformed through 4 operations: SubBytes, ShiftRows, MixColumns and Add-RoundKey. The final round (10, 12, or 14 depending on the key size) does not perform MixColumns. The SubBytes operation replaces each byte by another byte according to a predefined lookup table. ShiftRows circularly rotates row i to the left by i. MixColumns is a linear transformation of the columns with bytes interpreted as elements of  $\mathrm{GF}(2^8)$ . AddRoundKey performs an exclusive-or with a round key. Note that SubBytes is the only non-linear transformation.

AES-NI. The Advanced Encryption Standard instruction set (AES-NI) is an extension of the x86-64 instruction set, which implements the steps of the AES encryption. It offers both better performance and enhanced security than software implementations. For AES encryption, AES-NI supports two main instructions: AESENC, which performs a full AES round consisting of SubBytes, ShiftRows, MixColumns, and Add-RoundKey, and AESENCLAST, which performs SubBytes, ShiftRows, and AddRoundKey for the last round.

#### B. PoC Attack Overview

The high-level idea behind the attack is to train the branch prediction unit (BPU) to speculatively exit the AES implementation after performing fewer rounds than required. We flush the key length from the cache then invoke the encryption. The BPU predicts which branches to take in the implementation and by extension predicts how many rounds to apply. Because it takes time for the processor to retrieve the key length from the memory, the processor does not immediately detect the misprediction, allowing the code to return speculatively to the attacker, who then leaks the ciphertext via a cache-based covert channel. At some later time, the processor retrieves the correct number of rounds and squashes all of the mispredicted execution, including any later execution of the attacker. It then restarts execution from the first mispredicted branch, completing the correct number of rounds. However, squashing instructions does not revert any changes made to the cache. This allows an attacker to measure the state of the cache using

the FLUSH+RELOAD attack [53] and retrieve the partially encrypted ciphertext.

#### C. PoC Attack on AES

We begin with a description of our PoC attack on Listing 3. The aes\_round and aes\_final\_round functions are backed by compiler intrinsics that replace the functions with the AESENC and AESENCLAST instructions. The key variable contains the full key expansion along with the number of rounds that needs to be performed.

Step 1: Branch Predictor Training. Our goal in this attack is to train the branch history buffer, which predicts the conditions of conditional branches, to abort the encryption early, allowing the attacker to leak the ciphertext for a reduced-round AES that can be cryptanalyzed to recover the key. Listing 4 shows the pseudocode of the attack. It starts by creating two keys, one which trains the BPU and one which emulates a secret key the attacker does not have access to. We repeatedly call encrypt using the training key, training the BPU to predict false for the condition on line 17 in Listing 3. This causes encrypt to exit after applying ten rounds. We note that in practice, an attacker can use other means to train the BPU. In particular, the attacker can rely on aliasing in the BPU, using a branch that the attacker controls to train prediction within encrypt.

Step 2: Triggering Misspeculation. After training the branch predictor, we flush the field key. rounds from the cache. The field controls the branches on lines 17 and 20 of Listing 3 which control the number of rounds to apply. Thus, flushing it from the cache delays the evaluation of these branches until the field is retrieved from memory. Until that time, the processor uses the false prediction for the condition on line 17, as trained earlier, and proceeds speculatively along the mispredicted execution path. This delay is necessary to allow the speculative execution to perform the final round (Listing 3, line 25) and return to the attacker code, which leaks the roundreduced ciphertext through a microarchitectural side channel (Listing 4, line 12). Eventually, the processor will retrieve key rounds from the memory, perform the comparisons for the conditions, detect that the branch was mispredicted, squash the ensuing speculative execution, and resume execution with the correct true condition in line 17. However, by this time, the reduced-round ciphertext has already leaked through the side channel.

Step 3: Recovering the Reduced-Round Ciphertext. Finally, execution once again returns from encrypt and control flows to sidechannel\_recv. This function acts as the receiver of the side channel and receives the reduced-round ciphertext from the transiently executed sidechannel\_send. We implement sidechannel\_recv using FLUSH+RELOAD [53], a cache side-channel that can determine if a particular address has been accessed. We leak the incorrect ciphertext one byte at a time, by selecting a byte and using it to access a 256-page array. We can then check which of the 256-pages has been accessed to recover one byte of the reduced-round ciphertext from the

previously squashed execution. This process is repeated for each of the 16 bytes of the reduced-round ciphertext. We note that multiple side channels have been demonstrated in the context of transient-execution attacks [4, 12, 24, 40], and the choice of channel is not limited to FLUSH+RELOAD.

**Attack Accuracy.** We test two victims. The first uses a default LLVM back-end for code generation and the second uses LLVM with SLH enabled. We repeat the attack 1 000 times with each victim, each time recording whether the reduced-round ciphertext is recovered correctly. On average the attack succeeds with a probability of 95% irrespective of the victim.

# D. PoC Attack on OpenSSL AES

We further demonstrated leakage from two AES implementations provided in OpenSSL. The first implementation uses T-tables for implementing the round function and the second uses AES-NI. The T-table implementation follows the same general structure of the FaCT implementation in Listing 3, but uses precomputed tables for performing the round function. The T-table implementation is known to be vulnerable to cache attacks [36], but our PoC does not exploit this vulnerability. Instead, we use the same strategy as in Listing 4, recovering the round-reduced ciphertext. When SLH is disabled, the PoC works as expected. Enabling SLH prevents the leak because SLH poisons the table accesses executed in the last round.

The second implementation we test is the default OpenSSL implementation for computers that support AES-NI. The implementation, which is written in x86-64 assembly, uses the AESENC instruction in a loop, and then invokes AESENCLAST for the last round. To determine the number of iterations, the implementation uses the value of key.rounds. Our PoC trains the loop to stop after one iteration, resulting in a two-round encryption. We only test this implementation without SLH, because LLVM SLH does not apply to assembly code. Appendix B describes how to recover the key from the information we obtain.

# E. Attack Practicality

The proof-of-concepts we present in this section serve to show that ignoring declassification can result in leakage from otherwise protected code. Several aspects may make our attacks difficult in practice. Specifically, while intra-process isolation is an active research area [29, 48, 50], some real-world applications seem to be moving in the opposite direction [39]. To perform the attack across process boundaries, the attacker will have to overcome branch predictor flushing in modern processors and to find a leaky gadget that leaks the mispredicted declassified values. The former could be achieved through confused deputy attacks [6] and the latter through automated search of vulnerable gadgets [12]. We leave implementing these to future work.

```

export void unrolled_fact (secret uint64[2] plaintext,

1

2

public mut uint64[2] ciphertext, mut AES_KEY key) {

3

secret mut uint64<2> state = load_le(plaintext);

secret mut uint64<2> rd_key = load_le(view(key.rd_key, 0, 2));

4

public uint32 rounds = uint32(key.rounds);

assume(rounds < 15);</pre>

6

state = state ^ rd_key;

rd_key = load_le(view(key.rd_key, 2, 2));

7

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 4, 2));

8

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key,

Q

rd_key = load_le(view(key.rd_key, 8, 2));

10

state = aesenc(state, rd_key);

state = aesenc(state, rd_key);

rd_key = load_le(view(key.rd_key, 10, 2));

11

state = aesenc(state, rd_key);

rd_key = load_le(view(key.rd_key, 12, 2));

12

13

state = aesenc(state, rd_key);

rd_key = load_le(view(key.rd_key, 14, 2));

state = aesenc(state, rd_key);

rd_key = load_le(view(key.rd_key, 16, 2));

14

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 18, 2));

15

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 20,

16

if (rounds > 10) {

17

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 22, 2));

18

19

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 24, 2));

20

if (rounds > 12) {

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 26, 2));

21

state = aesenc(state, rd_key); rd_key = load_le(view(key.rd_key, 28, 2));

22

23

}

24

state = aesenclast(state, rd_key);

25

store_le(ciphertext, declassify(state));

26

27

```

Listing 3: FaCT implementation of unrolled AES encryption. The aesenc and aesenclast functions are compiler intrinsics that map to the AESENC and AESENCLAST x86 instructions.

```

function attack() {

1

2

training_key = create_aes128_key();

3

secret_key = create_aes192_key();

4

for (int i = 0; i < 127; i++) {

5

encrypt(plaintext, training_key);

6

8

flush (secret_key.rounds);

9

ciphertext = encrypt(plaintext, secret_key);

10

11

12

sidechannel_send(ciphertext);

13

return sidechannel recv():

14

15

```

Listing 4: Pseudocode of our attack on AES. For clarity, we show training and victim execution as separate steps. In practice, our code does both of these steps in the same loop, using constant-time select to switch between inputs.

#### VIII. RELATED WORK

**Robust Declassification.** Relative non-interference is closely related to *robust declassification* [54].<sup>2</sup> Robust declassification requires that active attackers—formalized as adversarial transition steps—do not observe any more information from a program than passive attackers. Although the definition of robust declassification predates Spectre attacks by nearly two decades, it can be instantiated to our setting: The labeling of registers and arrays in our setting corresponds to their lattice

of security domains, and their equivalence classes of states at each transition step are represented by our sequences of observations O. Passive attackers correspond to sequential executions limited to step transitions, while active attackers correspond to speculative executions governed by adversarial directives  $d \in Dir$ . Under this framework, robust declassification states that if the sequential execution of any two initial states produces equivalent observations, then the speculative traces must produce equivalent observations as well. Our definition of RNI only depends on the *sequential prefix* of the speculative traces rather than a full sequential trace; Lemma 8 in Appendix A shows that our notion is stronger than the alternative 4-executions notion which considers two full sequential execution traces and two full speculative execution traces.

Information Flow and Constant-time. There is a significant body of work on information flow and declassification, see e.g., [42, 44]. Sabelfeld and Myers [43] introduce delimited information release, and show how it can be enforced by a classic information-flow type system. We model security of countermeasures in a spirit that is close to delimited release. However, their formal definition only considers sequential semantics, whereas our definition contrasts sequential and speculative semantics. In addition, we reason about leakage, whereas (as is common for information-flow type systems) they reason about equality of outputs.

There is a growing body of work that uses type systems and static program analyses to enforce that programs are constant-time; see [7] for a recent survey. However, these works either do not consider or do not provide guarantees for declassification.

<sup>2&</sup>quot;Declassification" in their setting corresponds to all leakages—not just decl observations—in ours.

The only exception is [3], which supports public outputs. Public outputs are a form of declassification that is required by cryptographic libraries, e.g., to leak the length of a string. However, [3]'s focus on declassification is complementary to ours: they show how to relax the verification algorithm so that leaks that do not reveal more than the public output are not considered insecure; their relaxation allows for more efficient code to be written. Our work provides instead a means to protect against unintended leakage caused by speculative execution.

**Speculative Semantics.** There is a growing body of work that applies language-based techniques to reason about security under speculative execution; see [17] for a recent survey. Our adversarial semantics is inspired by [16] and by [9]; however, we refine their adversarial directives: Attackers in their semantics explicitly specify which direction each branch speculates, e.g., with directives like force T, and so may not always misspeculate. In contrast, our force directive always takes the incorrect branch, letting us easily delineate misspeculated execution and simplify our proofs. In addition. our semantics differs from [9] in its treatment of unsafe memory accesses: Indeed, the semantics of [9] immediately aborts execution and leaks the complete memory whenever an unsafe access is performed. Their semantics is thus too coarse for reasoning about the security of our countermeasure (or speculative load hardening). In contrast, our semantics resolves unsafe memory accesses with adversarial directives.

Prior semantics serve as the basis for defining security of applications under speculative execution. These speculative security properties fall into two categories: Direct and relative properties [17]. Direct notions, such as speculative constant-time [16], are specified as 2-trace non-interference hyperproperties, and prevent (explicitly typed) secret data from leaking to an attacker. Relative notions, such as speculative non-interference (SNI) [27] and trace property-dependent observational determinism (TPOD) [19] instead simply prevent an attacker from learning more information than they would sequentially. These properties are thus typically specified in terms of four traces—two speculative traces for the leakage trace of the program, and two sequential traces to determine the baseline leakage to compare against. Our security property, RNI, is also a form of relative property; however, we require only two execution traces in our definition. As a result, it is stronger than 4-trace properties such as SNI: If a program satisfies RNI then it satisfies SNI. In addition, RNI explicitly handles declassification; we are not aware of any prior work that explicitly connects relative notions with declassification.

Blade [49] is an automated tool that eliminates speculative leaks via hardening loads or inserting fences. Their approach views secret inputs as sources and observations as sinks, and applies classic graph algorithms to infer where protections must be inserted. Their approach is evaluated on WebAssembly implementations of cryptographic algorithms.

Patrignani and Guarnieri [37] study the security impact of compiler transformations and countermeasures in a model of speculative execution. They propose two criteria, called robust speculative safety (RSS) and robust speculative non-interference

(RSNI), and evaluate proposed (both theoretical and deployed) countermeasures w.r.t. these criteria. One main difference with our work is that they emphasize *robust compilation*, i.e., properties that are preserved even when the program is linked with arbitrary code. Robustness is an important concern but is not considered in our work. Another key difference is that our language features an explicit construct with declassification; this construct is essential in our setting to capture programmer's intent, but not considered in [37].

# IX. CONCLUSION

Using AES as a concrete example, we have showed that speculative execution may leak more information than intended by programmers, *even if* programs are protected with SLH. We have also proposed a countermeasure based on Selective Speculative Load Hardening (SelSLH) to ensure that programs do not leak beyond programmer's intent. Preliminary evaluations suggest that SelSLH is of independent interest and can drastically reduce the overhead of protecting against Spectre-PHT. One exciting direction of work is to implement SelSLH in an existing framework for efficient high-assurance cryptography and build an efficient, formally verified crypto library that achieves the guarantees offered by RNI.

# ACKNOWLEDGEMENTS

This research was supported by the Air Force Office of Scientific Research (AFOSR) under award number FA9550-20-1-0425; an ARC Discovery Early Career Researcher Award (project number DE200101577); an ARC Discovery Project (project number DP210102670); the Blavatnik ICRC at Tel-Aviv University; the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA; the Deutsche Forschungsgemeinschaft (DFG, German research Foundation) as part of the Excellence Strategy of the German Federal and State Governments – EXC 2092 CASA - 390781972; the European Commission through the ERC Starting Grant 805031 (EPOQUE); the National Science Foundation under grant CNS-1954712; and gifts from AMD, Google, Intel, and Qualcomm.

# REFERENCES

- Onur Actiçmez, Çetin Kaya Koç, and Jean-Pierre Seifert. Predicting secret keys via branch prediction. In CT-RSA, pages 225–242, 2007. 2,

- [2] Alejandro Cabrera Aldaya, Billy Bob Brumley, Sohaib ul Hassan, Cesar Pereida García, and Nicola Tuveri. Port contention for fun and profit. In *IEEE SP*, pages 870–887, 2019. 4

- [3] José Bacelar Almeida, Manuel Barbosa, Gilles Barthe, François Dupressoir, and Michael Emmi. Verifying constant-time implementations. In *USENIX Security*, pages 53–70, 2016. URL https://www.usenix.org/conference/usenixsecurity16/technical-sessions/presentation/almeida. 13

- [4] Ben Amos, Niv Gilboa, and Arbel Levy. Spectre without shared memory. In SAC, pages 1944–1951, 2019. 11

- [5] Aslan Askarov, Daniel Hedin, and Andrei Sabelfeld. Cryptographically-masked flows. In SAS, pages 353–369, 2006. doi: 10.1007/11823230\\_23. URL https://doi.org/10.1007/11823230\_23. 1

- [6] Enrico Barberis, Pietro Frigo, Marius Muench, Herbert Bos, and Cristiano Giuffrida. Branch history injection: On the effectiveness of hardware mitigations against cross-privilege Spectre-v2 attacks. In USENIX Security, 2022. 11

- [7] Manuel Barbosa, Gilles Barthe, Karthik Bhargavan, Bruno Blanchet, Cas Cremers, Kevin Liao, and Bryan Parno. Sok: Computer-aided cryptography. In *IEEE SP*, pages 777–795, 2021. 12

- [8] Gilles Barthe, Gustavo Betarte, Juan Diego Campo, Carlos Daniel Luna, and David Pichardie. System-level non-interference for constant-time cryptography. In CCS, pages 1267–1279, 2014. doi: 10.1145/2660267. 2660283. URL https://doi.org/10.1145/2660267.2660283. 4

- [9] Gilles Barthe, Sunjay Cauligi, Benjamin Grégoire, Adrien Koutsos, Kevin Liao, Tiago Oliveira, Swarn Priya, Tamara Rezk, and Peter Schwabe. High-assurance cryptography in the spectre era. In *IEEE SP*, pages 1884–1901, 2021. 3, 5, 13

- [10] Daniel J. Bernstein. Curve25519: new Diffie-Hellman speed records. In PKC, pages 207–228, 2006. Document ID: 4230efdfa673480fc079449d90f322c0, http://cr.yp.to/papers.html# curve25519. 8

- [11] Daniel J. Bernstein, Tanja Lange, and Peter Schwabe. The security impact of a new cryptographic library. In *LATINCRYPT*, pages 159–176, 2012. http://cryptojedi.org/papers/#coolnacl. 8

- [12] Atri Bhattacharyya, Alexandra Sandulescu, Matthias Neugschwandtner, Alessandro Sorniotti, Babak Falsafi, Mathias Payer, and Anil Kurmus. SMoTherSpectre: Exploiting speculative execution through port contention. In CCS, pages 785–800, 2019. 11

- [13] Claudio Canella, Jo Van Bulck, Michael Schwarz, Moritz Lipp, Benjamin von Berg, Philipp Ortner, Frank Piessens, Dmitry Evtyushkin, and Daniel Gruss. A systematic evaluation of transient execution attacks and defenses. In USENIX Security, pages 249–266, 2019. 3